单位代码: 10359

学号: 2017170834

密级: 公开

分类号: TN47

合肥工业大学

Hefei University of Technology

**硕士学位论文**

**MASTER'S DISSERTATION**

**(专业硕士)**

论文题目: AMOLED 驱动中的伽马校正电路

的研究与设计

学科专业: 集成电路工程

作者姓名: 庄则敬

导师姓名: 尹勇生 研究员

孙晓霞 副教授

完成时间: 2020 年 6 月

合 肥 工 业 大 学

学历硕士学位论文

**AMOLED 驱动中的伽马校正电路的研究

与设计**

作者姓名: 庄则敬

指导教师: 尹勇生 研究员

孙晓霞 副教授

学科专业: 集成电路工程

研究方向: 集成电路设计与测试

2020 年 6 月

A Dissertation Submitted for the Degree of Master

**Study and Design of GAMMA correction Circuit in

AMOLED Driver Chip**

By

Zhuang Zejing

Hefei University of Technology

Hefei, Anhui, P.R.China

June, 2020

# 合肥工业大学

本论文经答辩委员会全体委员审查，确认符合合肥工业大学专业硕士学位论文质量要求。

答辩委员会签名（工作单位、职称、姓名）

主席：中国科学技术大学 教授 龙世君

委员：合肥工业大学 教授 陈立

合肥工业大学 副教授 倪伟

合肥工业大学 副教授 程山

合肥工业大学 副教授 宋晓东

导师：孙晓东

## 学位论文独创性声明

本人郑重声明：所呈交的学位论文是本人在导师指导下进行独立研究工作所取得的成果。据我所知，除了文中特别加以标注和致谢的内容外，论文中不包含其他人已经发表或撰写过的研究成果，也不包含为获得 合肥工业大学 或其他教育机构的学位或证书而使用过的材料。对本文成果做出贡献的个人和集体，本人已在论文中作了明确的说明，并表示谢意。

学位论文中表达的观点纯属作者本人观点，与合肥工业大学无关。

学位论文作者签名：庄则敬

签名日期：2020年6月30日

## 学位论文版权使用授权书

本学位论文作者完全了解 合肥工业大学 有关保留、使用学位论文的规定，即：除保密期内的涉密学位论文外，学校有权保存并向国家有关部门或机构送交论文的复印件和电子光盘，允许论文被查阅或借阅。本人授权 合肥工业大学 可以将本学位论文的全部或部分内容编入有关数据库，允许采用影印、缩印或扫描等复制手段保存、汇编学位论文。

（保密的学位论文在解密后适用本授权书）

学位论文作者签名：庄则敬

指导教师签名：孙晓农

签名日期：2020年6月30日

签名日期：2020年6月30日

论文作者毕业去向

工作单位：

联系电话：

E-mail：

通讯地址：

邮政编码：

# 致谢

三年的研究生生涯即将结束，在这三年中，我学到了很多东西，在论文完成之时，我要向在生活和学习中给予我帮助的人表达感谢之情。

首先感谢微电子设计研究所为我提供一个良好的学习和科研平台，让我在集成电路研究领域能有充分的学习条件，使我在这三年里学习到很多专业知识，熟悉 EDA 工具的使用，对集成电路产生出更多的兴趣。

感谢我的研究生导师尹勇生教授和孙晓霞副教授在我生活和学习方面给予的关心和帮助，尹老师丰富的专业知识，严谨的教学态度和宽广的科研眼光给了我很多的启发，孙老师的指导给我明确的研究方向，坚定了我在集成电路领域深入研究的决心。感谢邓红辉副教授在我科研和论文写作方面的指导，邓老师耐心指导我的学习，在论文写作方面给予了我细致的修改，使我的论文写作更加顺畅。

感谢微电子研究所的陈红梅，孟煦，木子一，范月红以及胡剑老师等各位老师在我研究生生涯生活和学习方面给予的指导和帮助。

感谢 OLED 项目组的贾晨老师和权磊，吴景生学长在生活和项目学习中的指导，跟着你们我学习到了更多的知识，更拓宽了视野。

感谢项目组的宇跃峰，孙蕊，马奔，陈昕宇，张宇航，钱希琛在学习上的交流和指导，正因我们的合作，才让项目能更好的进行下去。

最后，我要感谢我的家人，感谢他们对我的支持，正是他们的支持与理解，才让我完成研究生阶段的学习，取得今天的成果。

作者：庄则敬

2020 年 6 月

## 摘要

近些年，OLED 技术已经成为显示面板厂商眼中的新宠，使用该技术的设备以体型轻薄，发热量低，画质精细等优点风靡全球。伽马校正技术通过 DAC 调节显示曲线，提高灰阶电压精度，对 OLED 显示效果的好坏有着非常重要的影响。

本文研究并设计了基于分辨率在 1080\*2220，具备 1670 万色的 AMOLED 显示屏的伽马校正电路。论文结合 AMOLED 驱动的基本原理，分别对其中的 VGMP/VGSP 电压产生电路，VGMP/VGSP 缓冲器电路功能以及拐点与输出缓冲器电路进行了分析和研究，并据此得出伽马校正电路应具备的参数性能和结构。为了保证共模输入电压的范围能够达到从电源到地，VGMP/VGSP 电压产生电路采用轨到轨输入级结构。而由于 VGMP/VGSP 缓冲器电路的共模输入摆幅较大，电路采用跨导恒定设计以稳定其工作状态。拐点与输出缓冲器电路为了提升负载驱动能力而使用 class AB 输出级，并通过使用 cascode Miller 补偿减小了缓冲器的面积。最后完成了伽马校正电路的版图设计。

论文基于 UMC 80nm 标准 CMOS 工艺对伽马校正电路进行仿真验证。通过对电路整体的级联仿真得到输出的灰阶电压精度为 3mV，系统响应时间为 20us 的较好性能。通过对各子电路分别仿真验证，得到 VGMP/VGSP 电压产生电路的相位裕度为 90 度、环路增益为 55dB，瞬态响应时间为 13us。VGMP/VGSP 缓冲器电路的相位裕度为 80 度，环路增益为 60dB，瞬态响应时间分别为 1.446us/1.235us。拐点与输出缓冲器电路的相位裕度为 75 度，环路增益为 129dB，当精度为 90% 的时候瞬态响应时间为 1.49us，当精度上升至 99.9% 的时候，瞬态响应时间为 3.5us。仿真结果表明，电路达到了预期的性能。对 VGMP/VGSP 输出缓冲器进行后仿真，结果表明和前仿真基本一致，满足设计要求。

关键词：AMOLED；伽马校正；LDO；输出缓冲器

## Abstract

In recent years, OLED technology has been a new favor of display panel manufacturers. The devices using this kind of technology have been popular all over the world with the advantages of lighter weight, thinner thickness, low power consumption and higher texture quality. GAMMA correction technology has decisive significance to the display effect of panel with adjustment of display curve and improvement of gray-scale voltage accuracy.

In this thesis, a Gamma correction circuit suitable for driving AMOLED display panel with 1080\*2220 resolution and 16.7 million colors is studied and designed. This thesis researched the structure and got the parameters of the VGMP/VGSP voltage generation circuit, VGMP/VGSP buffer circuit and breaking point output buffer circuit according to the fundamental principles of AMOLED driving theory. In order to keep the range of common mode input voltage from 0 to power supply voltage, VGMP/VGSP voltage generation circuit used the rail-to-rail input structure. The VGMP/VGSP buffer circuit used transconductance constant methodology to stabilize the output voltage for the high input swing. The breaking point buffer used class AB output stage to improve the load driving ability and cascode Miller compensation methodology to reduce the space occupation of the chip. Finally the layout design of GAMMA correction circuit is also accomplished.

This thesis did the simulation verification of the whole module based on the technology of UMC 80nm and got good performance with output voltage accuracy of 3mV and the total response time of 20us. The VGMP/VGSP voltage generation circuit got the phase margin of 90 degree, 55dB loop gain and 13us response time. VGMP/VGSP buffer circuit got the phase margin of 80 degree, 60dB loop gain and 1.446us/1.235us response time. The breaking point buffer got the phase margin of 75 degree, 129dB loop gain and 1.49us response time at 90% accuracy and 3.5us response time at 99% accuracy. The circuit can get expected performance according to the simulation result. The Post-simulation result of VGMP/VGSP output buffer agrees with the Pre-simulation result according to the simulation result.

**KEYWORDS:** AMOLED; Gamma correction; LDO; Output buffer

# 目录

|                                   |    |

|-----------------------------------|----|

| 第一章 绪论.....                       | 1  |

| 1.1 研究背景及意义.....                  | 1  |

| 1.2 国内外研究现状.....                  | 2  |

| 1.3 论文的主要工作和结构安排.....             | 4  |

| 第二章 OLED 显示原理和驱动方式.....           | 6  |

| 2.1 OLED 屏幕的发光原理 .....            | 6  |

| 2.2 OLED 的驱动方式 .....              | 8  |

| 2.2.1 无源驱动 (PMOLED) .....         | 8  |

| 2.2.2 有源驱动 (AMOLED) .....         | 9  |

| 2.3 本章小结.....                     | 10 |

| 第三章 伽马校正电路系统设计.....               | 11 |

| 3.1 AMOLED 显示驱动芯片系统概述 .....       | 11 |

| 3.2 伽马校正的原理及方案.....               | 13 |

| 3.2.1 伽马校正原理.....                 | 13 |

| 3.2.2 本文的伽马校正优化方案.....            | 15 |

| 3.3 伽马校正电路的系统设计.....              | 18 |

| 3.3.1 伽马校正电路的架构.....              | 18 |

| 3.3.2 伽马校正主体电路的系统设计.....          | 20 |

| 3.4 伽马校正电路的设计指标.....              | 23 |

| 3.4.1 系统指标需求 .....                | 23 |

| 3.4.2 伽马校正电路关键模块的设计指标 .....       | 23 |

| 3.5 本章小结.....                     | 25 |

| 第四章 伽马校正电路的设计与仿真.....             | 26 |

| 4.1 VGMP/VGSP 电压产生电路 .....        | 26 |

| 4.1.1 VGMP/VGSP 电压产生电路的设计 .....   | 26 |

| 4.1.2 VGMP/VGSP 电压产生电路的指标分析 ..... | 27 |

| 4.1.3 轨到轨输入级设计 .....              | 28 |

|                                    |    |

|------------------------------------|----|

| 4.1.4 VGMP/VGSP 电压产生电路的仿真与分析 ..... | 29 |

| 4.2 VGMP/VGSP 电压输出缓冲器电路 .....      | 33 |

| 4.2.1 VGMP 输出缓冲器电路设计 .....         | 33 |

| 4.2.2 VGSP 输出缓冲器电路设计 .....         | 34 |

| 4.2.3 跨导恒定电路设计 .....               | 36 |

| 4.2.4 VGMP 输出缓冲器的仿真和分析 .....       | 39 |

| 4.2.5 VGSP 输出缓冲器的仿真和分析 .....       | 43 |

| 4.3 拐点和输出缓冲器电路 .....               | 47 |

| 4.3.1 电路设计 .....                   | 48 |

| 4.3.2 Class AB 输出级设计 .....         | 49 |

| 4.3.3 Cascode Miller 补偿 .....      | 50 |

| 4.3.4 仿真分析 .....                   | 51 |

| 4.4 伽马校正电路的级联仿真 .....              | 55 |

| 4.5 伽马校正电路的版图及后仿 .....             | 58 |

| 4.5.1 伽马校正电路的版图设计 .....            | 58 |

| 4.5.2 后仿真 .....                    | 61 |

| 4.6 本章小结 .....                     | 63 |

| 第五章 总结与展望 .....                    | 64 |

| 5.1 总结 .....                       | 64 |

| 5.2 展望 .....                       | 64 |

| 参考文献 .....                         | 66 |

## 插图清单

|                                      |    |

|--------------------------------------|----|

| 图 2.1 OLED 器件剖面结构 .....              | 6  |

| 图 3.1 AMOLED 驱动芯片架构 .....            | 11 |

| 图 3.2 显示器件输出特性 .....                 | 14 |

| 图 3.3 屏幕所需的灰阶—电压曲线 .....             | 14 |

| 图 3.4 线性数据结合非线性 DAC .....            | 15 |

| 图 3.5 非线性数据结合线性 DAC .....            | 15 |

| 图 3.6 R/G/B 像元校正 .....               | 17 |

| 图 3.7 本文提出的伽马校正方案 .....              | 18 |

| 图 3.8 伽马校正电路架构 .....                 | 19 |

| 图 3.9 灰阶电压曲线的分段线性化 .....             | 20 |

| 图 3.10 关键灰阶电压产生过程 .....              | 21 |

| 图 3.11 伽马校正主体电路结构 .....              | 21 |

| 图 4.1 VGMP/VGSP 产生电路结构图 .....        | 26 |

| 图 4.2 轨对轨输入级结构 .....                 | 28 |

| 图 4.3 输出电压 VGMP .....                | 29 |

| 图 4.4 输出电压 VGSP .....                | 30 |

| 图 4.5 VGMP/VGSP 产生电路 STB 分析 .....    | 31 |

| 图 4.6 输出电压 VGMP 电源抑制比 .....          | 32 |

| 图 4.7 VGMP/VGSP 电路启动过程仿真 .....       | 32 |

| 图 4.8 VGMP 输出缓冲器电路结构 .....           | 33 |

| 图 4.9 VGMP 输出缓冲器的运算放大器电路 .....       | 34 |

| 图 4.10 VGSP 输出缓冲器电路结构 .....          | 35 |

| 图 4.11 VGSP 运算放大器电路 .....            | 35 |

| 图 4.12 轨对轨输入级结构 .....                | 36 |

| 图 4.13 总跨导与共模输入电压的关系 .....           | 36 |

| 图 4.14 偏置电路 .....                    | 37 |

| 图 4.15 VGMP 输出缓冲器电路的主运放结构 .....      | 37 |

| 图 4.16 VGMP 输出缓冲器电路的主运放结构（高电平） ..... | 38 |

| 图 4.17 VGMP 输出缓冲器电路的主运放结构（低电平） ..... | 38 |

|                                         |    |

|-----------------------------------------|----|

| 图 4.18 VGMP 输出缓冲器电路的主运放结构（中间电平） .....   | 39 |

| 图 4.19 VGMP 输出缓冲器的输出电压.....             | 39 |

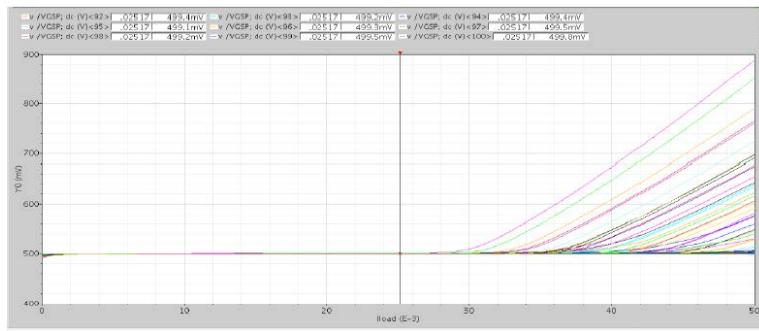

| 图 4.20 不同电源电压和 VGMP 电压下的负载电流 .....      | 40 |

| 图 4.21 VGMP 输出缓冲器电路稳定性分析.....           | 41 |

| 图 4.22 VGMP 输出缓冲器电路的电源抑制比.....          | 42 |

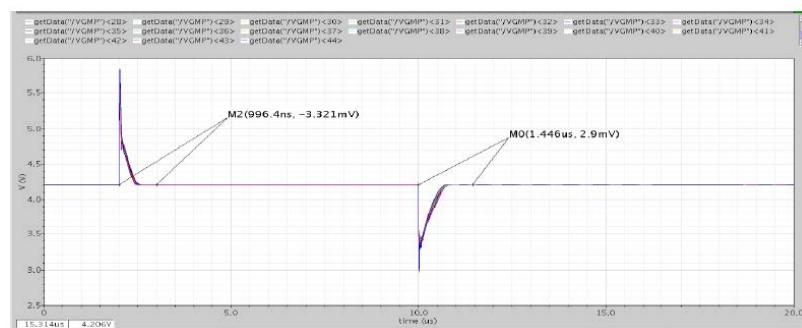

| 图 4.23 VGMP 输出缓冲器电路电源电压变化瞬态响应.....      | 42 |

| 图 4.24 VGMP 输出缓冲器电路的负载变化瞬态响应.....       | 43 |

| 图 4.25 VGSP 输出缓冲器电路的输出电压.....           | 43 |

| 图 4.26 VGSP 输出缓冲器电路的最大负载电流仿真.....       | 44 |

| 图 4.27 VGSP 输出缓冲器电路的稳定性仿真.....          | 45 |

| 图 4.28 VGSP 输出缓冲器电路的电源抑制比.....          | 46 |

| 图 4.29 VGSP 输出缓冲器电路电源电压变化瞬态响应.....      | 46 |

| 图 4.30 VGSP 输出缓冲器电路负载变化瞬态响应.....        | 47 |

| 图 4.31 VGMP 和 VGSP 输出缓冲器电路同时启动瞬态响应..... | 47 |

| 图 4.32 拐点与输出缓冲器电路.....                  | 48 |

| 图 4.33 Class AB 输出级.....                | 49 |

| 图 4.34 缓冲器等效小信号模型 .....                 | 51 |

| 图 4.35 不同输入电压下的电源抑制比 .....              | 52 |

| 图 4.36 不同输入电压下的稳定性仿真 .....              | 54 |

| 图 4.37 不同输入电压下的建立时间仿真 .....             | 55 |

| 图 4.38 伽马校正电路的启动时序 .....                | 55 |

| 图 4.39 DNL 和 INL 值仿真.....               | 56 |

| 图 4.40 伽马校正系统误差 .....                   | 57 |

| 图 4.41 伽马曲线仿真结果 .....                   | 57 |

| 图 4.42 伽马曲线误差比较 .....                   | 58 |

| 图 4.43 伽马校正电路的版图 .....                  | 59 |

| 图 4.44 VGMP 输出缓冲器的 PSRR .....           | 62 |

| 图 4.45 VGMP/VGSP 输出缓冲器的相位裕度.....        | 62 |

| 图 4.46 VGMP 输出缓冲器的增益.....               | 62 |

| 图 4.47 VGSP 输出缓冲器的增益.....               | 63 |

## 表格清单

|                                   |    |

|-----------------------------------|----|

| 表 2.1 AMOLED 与 PMOLED 驱动方式对比..... | 9  |

| 表 3.1 伽马校正方案对比 .....              | 16 |

| 表 3.2 伽马校正整体设计指标 .....            | 23 |

| 表 3.3 VGMP/VGSP 产生电路的设计指标 .....   | 23 |

| 表 3.4 VGMP/VGSP 缓冲器电路的设计指标.....   | 24 |

| 表 3.5 伽马拐点与输出缓冲器的设计指标 .....       | 24 |

# 第一章 绪论

## 1.1 研究背景及意义

随着人类社会的不断发展，显示器逐渐深入人们的日常生活中。显示技术经过了多代的发展，最早出现的是 CRT 管，CRT 技术起源于 100 多年前，是最早发明的显示技术。CRT 显示技术具有显示彩色色域宽，像素数可变易于调节分辨率，像素位置不固定，显示斜线更平滑等优点。但随着信息革命的逐渐深入，以晶体管为基础的超大规模集成电路的广泛应用，电子产品更加看重小体积，高性能，低功耗，复合功能等方向。CRT 技术存在的体积庞大，重量高，电压需求高等缺点就日益凸显，渐渐退出主流市场。与此同时 LCD 所具有的低功耗，小体积，低辐射以及低失真取而代之，占据了市场主流<sup>[1-2]</sup>。如今 LCD 已经成为了一种成熟技术，在各个领域得到运用。但它存在的很多缺陷和不足制约了它的发展前景。比如 LCD 屏的可视偏转角度小，容易产生影像拖尾现象，亮度和对比度不是很好等问题。此时出现的 OLED 技术是一种基于有机材料主动发光的二极管。和前辈比起来，它具有更低的功耗，采用柔性结构的可能，以及更广的视角。在现今得到各大厂商和用户的喜爱，进入发展的快车道<sup>[3]</sup>。

随着平板技术的不断发展，相关消费品的市场竞争也愈加激烈。平板显示正在经历从 LCD 向 OLED 的技术转变。OLED 成为未来面板技术最重要的发展方向。随着智能终端的不断普及，用户对屏幕的功能性方面也有了更加多样化的需求。OLED 显示面板有色彩丰富、反应迅速、分辨率高，颜色转换柔和以及可折叠等多项优点。具体来讲，与其它 FPD 相比，使用 OLED 的设备体型更轻巧，显示质量更清晰，发热更少，色彩覆盖更广，亮度调节能力优秀，画面转换过渡柔和不突兀。而与当今主流产品所使用的 LCD 屏幕相比，其重量轻，在用料和工时上能省去三分之一。因此，OLED 的综合生产成本要比 LCD 至少降低五分之一，在生产成本和产品性能上具有很强的优势。更加独特的是，OLED 产品可实现软屏。

OLED 屏幕按照不同的分类方法，也可以被划分出不同的种类。根据面板中像素电路的驱动方式划分，能够划分出 PMOLED 与 AMOLED 两大类<sup>[4-5]</sup>。使用 PMOLED 技术的屏幕没有使用完整的像素电路，只以一个个二极管组成阵列形成像素面板。二极管两级分别连接行，列驱动信号控制电路，电路导通则二极管在短时间内流

过大电流，完成发光过程。此方法对工艺要求较低，结构也偏简单，但缺点也很明显，功耗偏高，且输出精度受限。在高分辨率条件下的图像显示效果表现很差，因此使用范围受到很大限制。而 AMOLED 技术则使用电容和薄膜晶体管组成的像素电路构成发光阵列。该方法的每个像素电路独立受控开启，且电容能够存储信号，使得发光更为持久。该方法与 PMOLED 相比在发光效率和器件寿命上具有明显的优势，所以多用于大屏幕高分辨率的产品上，在目前的主流消费级电子产品如手机，电脑上，AMOLED 屏幕的使用率最高。

AMOLED 显示器件巨大的市场潜力，使得驱动电路的设计变得非常关键，驱动电路设计的优劣会极大影响显示效果和功耗<sup>[6]</sup>。随着 AMOLED 分辨率的提高，即意味着像素电路的数量增加，需要更多的行列驱动信号去控制。因此也需要电路具备更快的反应速度，这就对驱动电路性能提出很高要求。对于 AMOLED 驱动电路中的伽马校正电路而言，需要更高的性能来驱动后级的源极驱动电路，使驱动电路达到更高的精度和更快的响应速度，以适配更高分辨率的 AMOLED，使其有更好的显示效果。高性能的伽马校正电路对 AMOLED 驱动电路具有重要意义。

## 1.2 国内外研究现状

最早的有机质发光的现象在 1930s 就已经被人发现<sup>[7]</sup>，但得到重视并开始研究起源于邓青云博士。他于 1979 年在柯达公司工作时发现了 OLED 的存在。在 1987 年，柯达公司的研究团队利用低电压刺激二极管结构的有机材料发光，找到了 OLED 技术实用化的途径，为该公司接下来推出一系列 OLED 产品奠定了基础<sup>[8]</sup>。

由于伽马校正技术对 OLED 面板的显示效果起着决定性的作用，全世界的工程师和技术专家们都在加紧挖掘伽马校正技术的潜力，力求达到更好的显示效果。通过对前人发表的论文期刊进行研究，可以发现在常用移动设备例如手机，笔记本电脑上已经有较多的伽马校正方法得到了应用实践。

国内外科研人员在显示面板的伽马校正方面已经取得了不少突破。比如韩国的 Kim Eui Tae<sup>[9]</sup>构思出一种利用显示面板发出光的强度来分配灰阶电压的基于数字控制的伽马校正方案。先通过使用反馈机制测试一块未经伽马校正的面板在以一定规律变化的灰阶电压下发光，并得到该条件下的亮度曲线。然后对第二块面板使用非线性 DAC 进行插值操作得到另一条亮度曲线。根据理想的人眼感知亮度的曲线，将二者拟合直到最终找到亮度与灰阶电压一一对应的关系曲线。另外一名科研人员 Haeng Won Park<sup>[10]</sup>则另辟蹊径，使用一种动态电压的方法来处理伽马曲线，使电压和亮度形成一种动态平衡，灰阶电压可以随着亮度变化而发生实时变化。这种方法利用多通道的 DAC 产生灰阶电压以使其能够适应动态变化的

需要。Kaida Xiao 和 Chengyang Fu 等人<sup>[11]</sup>则使用人眼感知亮度的曲线结合公式法计算出亮度对应灰阶电压的值，然后通过插值法实现。Seung woo Lee<sup>[12]</sup>则通过先得到理想伽马校正曲线，再通过子像素混合法减小误差使实际曲线尽量与理想曲线靠拢，这种方法也做到了完善显示效果的作用。

在实际生产中可以发现，AMOLED 面板所使用的伽马校正模块与传统 LCD 屏幕的设计思路上有很多共通之处。在此基础上，2003 年 Tetsuro Itakura 和 Hironori Minamizaki 等人基于 0.6um 工艺，5V 电源电压的 LCD 显示驱动芯片。这种芯片总共可以提供 402 个灰阶电压，还特别针对像素电路的红绿蓝三种发光模式优化了驱动电流大小以达到低功耗的效果<sup>[13]</sup>。2005 年，Jang Woo Ryu 等设计了一款使用电压型 DAC 控制伽马曲线的驱动芯片，相比于过去的电流驱动型芯片大大加快了相应速度<sup>[14]</sup>。2007 年，Soo-yang Park 等人基于 0.3um 工艺设计出了一种精度为 8bit 的高速低功耗伽马校正方案。这种驱动芯片大量使用了轨到轨的结构，极大的降低了所需的电源电压<sup>[15]</sup>。2005 年，南台科技大学的 Po-Ming Lee 和 Hung-Yi Cheng 在他们发表的 Adjustable Gamma Correction Circuit for TFT LCD 中提出了新的伽马校正方案。即使用线性 DAC 调节非线性数据的思路。这种方法与过去的基于非线性 DAC 的调节法比起来，能够显著降低电阻的使用。这种方法大大降低了伽马校正电路的复杂程度，减小了功耗和芯片面积的浪费，在伽马校正思路的优化过程中有着重要的意义<sup>[16]</sup>。2009 年，台湾省科研人员 Jia-Hui Wang、Hao-Yuan Zheng 和 Chen-Huang Tsai 等设计了一种使用电流正反馈加上轨到轨结构的缓冲器电路。这种缓冲器使用了 0.35um 工艺，在电路内部的静态电流很小的情况下仍然能够输出大电流驱动极高负载。在这种情况下仍然能达到 5us 以内的建立时间，使得芯片的反应速度大大加快<sup>[17]</sup>。

国内业界工程师在通过伽马校正完善面板显示效果方面也积累了不少经验，如姚军才，何军峰等<sup>[18]</sup>工程师以大量的专业仪器产生的测试数据为基础，利用软件模拟出了不同的灰阶电压与亮度的对应关系，为图像处理工作建立起了一套固定的实验流程。叶达文<sup>[19]</sup>则基于显示控制原理，以 6bit 位宽的灰阶电压为基础对伽马校正的非线性 DAC 进行了改进优化，使得显示效果有了明显的提升。姜亨润<sup>[20]</sup>通过 16 个灰阶电压节点调节灰阶电压曲线的斜率，使用 DAC 改进了电压亮度之间的对应关系，实现了优化显示效果的作用。代永平<sup>[21]</sup>专注于高分辨率大屏幕显示面板的色彩优化，基于对伽马校正、亮度及色彩提出了一整套标准体系，并对该体系在医学及通信方面的运用做出了规范和预测。从以上事例可以看得出来，中国大陆在伽马校正技术方面的进步速度很快且已经产生了很多独到精妙的设计思路。但暴露出的问题也很多，比如这些方案多是针对已有设计产生问题的改进优化，本身并没有形成一套完整的伽马校正设计理论体系。这些理论多是停

留在实验阶段，并没有进入实际的生产实践。在实际的工业生产中，需要考虑成本和工序等问题。因而设计者需要在性能和成本方面做出取舍，拿出最实用化的方案，以便于形成产品投放市场。

从上面的研究成果可以看出，目前 AMOLED 驱动芯片技术主要来自于韩、日和台湾企业。现在主流的 AMOLED 驱动芯片的产品主要有韩国的三星、OLiGHTEK 和立迪思，港澳台地区的奇景光电、联咏、奕力科技、旭耀、晶门科技等。大陆的中颖电子和北方集创也在 AMOLED 显示驱动芯片方面积极布局。总的来讲，大陆方面还没有能够稳定供应 AMOLED 显示驱动芯片的公司。在显示驱动方面（含 LCD 驱动芯片）的市场占有率还比较低。大陆的最大驱动 IC 供应商的市场份额不大于 3%，在高端的显示驱动芯片方面，几乎为 0。这与我国显示面板生产大国的身份极不匹配。

目前我国相关行业与国内外先进水平还有着比较大的差距，特别是在高端驱动芯片方面。但从产业转移角度来看，平板显示产业正在从韩、日、中国台湾，慢慢向中国大陆聚集。而显示驱动芯片，是显示屏的刚需，是一个完整的平板显示产业所不可或缺的。可以预见，在未来的 5-7 年内，大陆必定会涌现出 2-3 家规模大于 10 亿甚至 20 亿的大型显示驱动芯片的企业。

随着消费者对搭载 AMOLED 产品的需求总量及消费能力的不断提高，AMOLED 面板将会往大尺寸、高分辨率、低功耗、宽可视角度、不规则形状、柔软易形变的方向发展<sup>[22-25]</sup>，其配套驱动芯片中的伽马校正电路也必须满足以下要求。

- (1) 更多的斜率调节点：更多的斜率调节点意味着伽马曲线更加贴近人眼感知曲线，像素电路能提供更加丰富的色彩显示，对伽马曲线更加精准的调节能力自然有了越来越高的要求。

- (2) 更强的驱动能力：更多的斜率调节点，会带来更多的电阻串，伽马校正电路能够做到在更短的时间内实现灰阶电压的准确输出，则必须要求驱动芯片驱动负载的能力相应提高。

- (3) 更低的功耗：对于设备往更加轻薄，更加便携的方向发展的大趋势，从设计指标的制定上应该更加倾向于降低功耗的方向。

### 1.3 论文的主要工作和结构安排

本文的目标是设计出分辨率为 1080\*2220、达到 1670 万色 AMOLED 显示驱动芯片的伽马校正电路。在研究 AMOLED 面板电路的驱动原理的基础上，确定合适的结构，并明确了各部分电路的设计指标和参数。驱动电路的伽马校正电路使用了非线性数据结合线性 DAC 的结构，由一个基准电压产生电路，幅度电压产生电

路以及输出缓冲电路组成。本文采用 UMC 80nm 工艺对电路进行设计，并完成了对伽马校正电路各功能模块的仿真与验证，整体版图设计和 VGMP/VGSP 输出缓冲器的后仿真。

本论文的结构安排如下：

第一章，绪论，阐述研究背景和意义，以及国内外研究现状，并对本文的主要工作和结构安排进行叙述。

第二章，分析 OLED 材料的发光原理，以及 OLED 驱动方案，包括无源驱动和有源驱动。

第三章，研究对比各种伽马校正方案，确定最适合本文需求的方案并据此设计电路结构，并根据需求确定各电路的设计指标。

第四章，对伽马校正电路中各个缓冲器和 LDO 进行详细分析。分别介绍了各个部分的设计需求，并设计出电路的整体结构。根据设计指标，设计了 VGMP/VGSP 电压产生电路，VGMP/VGSP 电压缓冲器电路和伽马拐点与输出缓冲器电路。并对各电路模块进行仿真验证。

第五章，总结与展望，对已完成的工作进行总结。同时提出改进意见以及可能的解决方案，为后续的研究指明方向。

## 第二章 OLED 显示原理和驱动方式

### 2.1 OLED 屏幕的发光原理

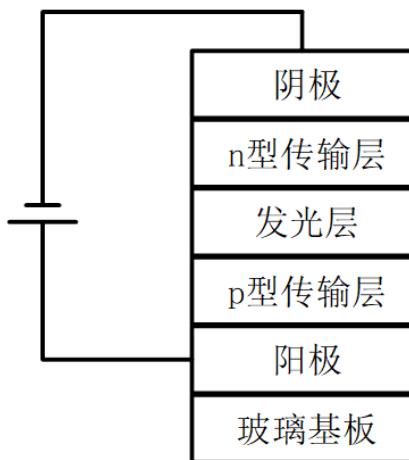

OLED 屏幕是使用有机材质导电后发光为工作原理的器件。图 2.1 是经典的 OLED 结构。

图 2.1 OLED 器件剖面结构

Fig 2.1 OLED device profile structure

从器件的截面图中可以看出，玻璃基板上首先被涂上一层阳极材料。这种半导体材料需要保持透明，对导电性也要求能有良好的特点，往往使用功函数高的 ITO 导电玻璃做阳极。ITO（氧化铟锡）玻璃的波长范围内为 400nm–1000nm 的有五分之四以上，且在近紫外区域的通过率也很高。OLED 的阴极材质着重增强了电子的注入效率，因为电子的注入难度比空穴更大，那么就能够尝试挑选功函数比较低的金属材料。金属功函数是评价金属导电能力的重要参数。金属功函数与导电性能成正比，较低的功函数能使得电子的注入更加方便，光强就更加可控。同时功函数也与发热有关，功函数越低，发出的热量就越少，可以延长使用寿命。

通常，阴极材料主要有三种。

第一，单层金属阴极。这种方法的优势是结构简单导电能力强，然而这些材料的化学属性不稳定，易被腐蚀，导致反应迟钝，寿命下降等问题。所以必须选择特殊的材料及隔离方法保证其化学性能稳定。

第二，合金阴极。为了保证发光的质量和化学性能的稳定，采用合金作为阴

极有其固有优势，比如合金薄膜在加工过程中会发生两种材料的相互混合，整个阴极兼具二者的优势，大大提高了抗腐蚀能力。

第三，层状阴极。该结构采用的是阻挡层法，在金属和电极之间覆盖上特殊的化合物，可以和金属电极组合成为双电极结构，大大提升其导电性。

OLED 电路从导通到发光的流程如下<sup>[26]</sup>。首先，打开电源，在发光材料两端建立开启电压。此时电路导通有电流流过有机材料，电源阴极会往有机材料的发射层传输电子，阳极则通过传导层接收阴极传送过来的电子。随后相遇的电子与空穴在二者的交界处大量复合，电子会填充入空穴中。最后复合瞬间的电子和空穴释放出光子使得 OLED 发光。OLED 发出光的色彩由有机分子层的材质决定，一般一块 OLED 屏幕上会铺设多层不同类型的有机材料。这些有机材料让显示器具备了发出多种颜色光的能力。光照的强度与流过有机材料的电流强弱有关，电流越大，光强也就越高。

为了让 OLED 屏幕有能力完整的发出所有颜色的光，构成较为逼真的色彩，往往采用两种手段。第一种是让 R（红）G（绿）B（蓝）三种像素电路各自独立发光。第二种是先发出白光，再利用滤光装置滤出需要的色彩。RGB 各自独立发光对色彩的还原度相比之下更胜一筹。在该电路中 RGB 三种发光电路在像素电路中各自独立运行独立发光。因此需要三种发光二极管，三种发光材料，这就造成了体积的巨大和成本的升高。而且对发光材料的加工精度也有较高要求，这造成了色彩控制方面的问题和寿命下降的问题。该类屏幕对亮度的设置存在瓶颈，且烧屏现象较为普遍，难以运用在使用大型屏幕的设备上。

第二种方法的重点在于滤光膜技术的使用。先发出白光，接着利用不同材质的滤光膜达成三原色的显示。该电路只需要一个能发出白光的二极管和一套驱动电路，通过在不同的二极管上覆盖不同的滤光膜形成全彩发光。该方法在工艺上只需要完成一种发光材料和三种滤光膜的生产，大大降低了加工难度，减少了成本，而且发白光的二极管可以做到发出更高的亮度和更长的寿命。因此该技术早在 LCD 时代就已经得到了广泛应用，多用于电视，电脑显示器等大面板和需要长时间使用的电子设备上。

对二者进行比较，很容易发现让像素电路独立发光可以在色彩上做到更加精细的调控。但加工难度过高，成本和寿命不尽人意限制了这种技术的广泛使用。而采用滤光片的白光二极管电路的成本较低，工艺更为简单，使用范围也更大，但相应的色彩显示质量较像素电路独立发光的 RGB 电路更差。

本文采用 RGB 子像素渲染技术，由红、绿、蓝自发光有机材料制作而成。在当前智能显示设备大尺寸、高分辨率的发展趋势下，制造极小且高密集度的 AMOLED 较为困难，成本较高，同时也导致驱动电路的结构过于复杂。因此，通过

改变子像素排列结构和减少子像素数量的方式可以有效解决这一问题。

## 2.2 OLED 的驱动方式

OLED 显示屏的发光机制和 LCD 时代的通过背光源发光以及 CRT 时代的通过射线发光有很大的不同, 按像素电路的结构和驱动模式不同具体可分为有源驱动和无源驱动两种。

### 2.2.1 无源驱动 (PMOLED)

PMOLED 的结构主要是由玻璃基板、ITO 阳极材料、有机发光材料和阴极共同组成的。其中, ITO 阳极和阴极与电源相连, 有机发光材料位于二者之间。当电路导通的时候电流流过有机材料, 来自阳极的空穴与来自阴极的电子在有机材料中复合, 放出能量使得有机材料发光。

有机材料的化学性质不稳定, 长时间暴露于空气和潮湿环境下容易改变化学属性, 因此封装过程需要严格保护。PMOLED 的薄膜厚度较小, 因此可以在数据板封装的时候加入干燥剂, 既保证了有机材料的性能, 也控制了厚度。

PMOLED 的驱动方式主要有动态和静态两大类。在动态驱动电路中, 像素单元的阳极和阴极组成矩阵结构, 阳极负责行像素的扫描, 阴极负责列像素的扫描。当电源导通向行像素单元的行扫描信号线施加上电压偏置信号后, 该行的发光二极管打开, 电流通过二极管导通整个回路使得二极管发光。在静态驱动电路中, 阴极是相互连接的而阳极是各自独立的。当需要某一个像素发光, 则只需要控制阳极电压, 使其与阴极的电压差大于开关电压, 二极管导通并发光。若需要关闭该管, 则只需将阳极接入负电压, 二极管截止。

人眼视网膜能够感知到的亮度通常是一段时间以内屏幕发出的光的平均亮度。对于一个 PMOLED 屏幕来说, 当电流相同的时候, 点亮的像素越多, 则每一个像素所分到的电流越少, 延长像素电路的反应时间, 降低瞬态亮度, 从而劣化了显示质量。因此, 如果需要显示的图像亮度大, 则需要发光二极管上流过的电流强度够高。与此同时带来的问题是大电流带来的高功耗, OLED 面板相比于 LCD 的低功耗优势就不再存在。而且高功耗带来的大量发热也会严重损害有机发光材料, 降低面板的寿命。此外, PMOLED 面板还有显示对比度差的问题。当行扫描信号施加的同时, 列驱动流过的电流在像素电路之间会发生漏电现象, 被称为串扰现象。所以在考虑面板设计指标的时候, 像素之间的距离, 像素的总数都有限制, 以便于达成较为理想的显示效果。因此, 对于需要使用大尺寸高分辨率的中高端设备, 往往不会采用 PMOLED 的显示方式。

### 2.2.2 有源驱动 (AMOLED)

与 PMOLED 相比, 有源驱动 AMOLED 的像素电路构造更为复杂。该驱动模式通过在玻璃面板上排列像素电路形成发光阵列, 再在其上层均匀涂抹有机发光材料, 最后通过布置金属导线和控制电路连成一体。AMOLED 的像素电路往往使用 TFT 薄膜晶体管做电路的驱动管产生驱动电流。同时, 每个像素电路中都会设置一个电容用来寄存从驱动电路传输来的数字信号。另外还会有一个薄膜晶体管成为开关决定像素电路的开启和关闭, 以控制显示相关信号是否进入驱动电路。AMOLED 在任何时候都只会打开一行, 并将图像信号存储在电容中。由于电容的存在, 即便此时开关电路没有导通, 该像素仍然能依靠电容中存储的信号发光, 减小了瞬间大电流对器件寿命和功耗方面的影响。因为由薄膜晶体管和电容组成的完整像素电路结构比二极管阵列结构更为复杂, 所以 AMOLED 面板对厂商的工艺水准提出了更高要求, 特别是薄膜晶体管的加工技术, 这就带来了更高的成本<sup>[27]</sup>。表 2.1 为 AMOLED 与 PMOLED 显示屏的比较。

表 2.1 AMOLED 与 PMOLED 驱动方式对比

Tab 2.1 Comparison of AMOLED and PMOLED driver mode

|      | AMOLED                    | PMOLED                 |

|------|---------------------------|------------------------|

| 驱动特性 | 像素独立驱动, 持续发光              | 瞬间通过大电流、高亮发光           |

| 显示方式 | 全彩色矩阵式                    | 单色彩色段式                 |

| 芯片位置 | TFT 驱动电路设计/内藏薄膜<br>型驱动 IC | 面板外附加 IC 芯片            |

| 扫描方式 | 线逐步式抹写数据                  | 线逐步式扫描                 |

| 成本功耗 | 低电压驱动/低耗电能/高成<br>本        | 低成本/高电压驱动              |

| 工艺制造 | 发光组件寿命长 (制程复杂)            | 设计变更容易、交货期短 (制<br>造简单) |

| 应用场景 | 大尺寸, 高分辨率, 高端产品           | 小尺寸, 低分辨率。低端产品         |

由此可知, 随着消费者对大尺寸高分辨率显示屏幕的偏好, PMOLED 技术逐渐落伍, 将来会慢慢退出市场。AMOLED 屏幕则会以依仗其全方位的优势占据市场主流, 在显示器件中的地位越来越举足轻重。

### 2.3 本章小结

本章主要说明了OLED面板发光的物理原理。首先分析了OLED面板的结构，面板的发光流程，构成各部分材料以及为了发出全色域光所采用的一些方法。接下来介绍了驱动OLED面板发光所需要的两种驱动方式AMOLED和PMOLED，分别阐述了AMOLED和PMOLED的驱动原理，从扫描方式、功耗、工艺成本、显示质量等多方面分别比较了各自的优点和不足。最后综合权衡后依据本文的需求选择了AMOLED的驱动设计。

## 第三章 伽马校正电路系统设计

### 3.1 AMOLED 显示驱动芯片系统概述

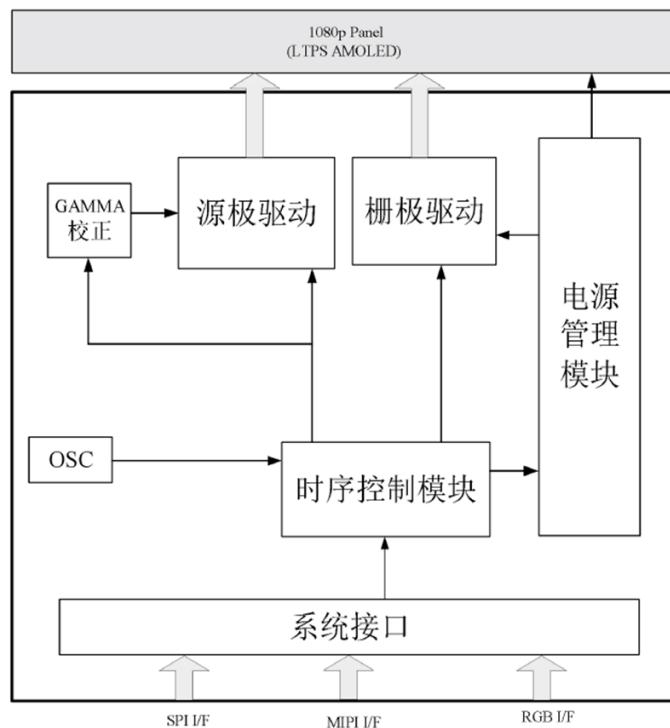

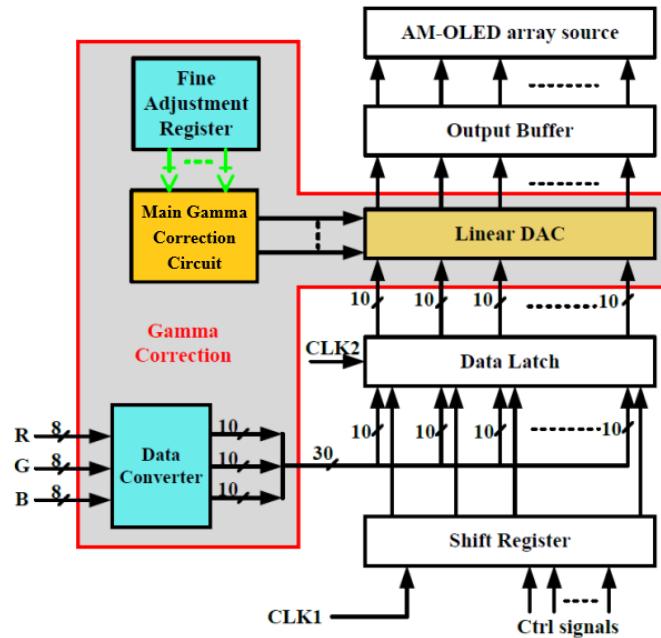

AMOLED 显示面板由驱动电路管理 OLED 的发光，因而需要设计合适的像素电路驱动芯片。图 3.1 是显示面板驱动电路的框图，主要有电源管理模块、源级驱动模块、栅极驱动模块、伽马校正电路、时序控制模块、振荡器和输入输出接口等。

图 3.1 AMOLED 驱动电路架构

Fig 3.1 The architecture of AMOLED driving circuit

由处理器产生的信号通过系统 I/O 接口向芯片内部传送数据和各种控制信息。这些信息在流入时序控制模块后与振荡器模块产生的时钟信号结合，产生用于控制电路栅源驱动的显示控制信号。通过接收这些信号栅极驱动电路就可以控制像素电路的开启和关断。而源级驱动信号则通过伽马校正电路的精细控制调整施加于像素电路的源级的电压大小完成对面板发光亮度的调节。电源管理模块则为以上所有功能模块提供正常运行时所需要的电源电压、输入电流、电压偏置和

基准等。驱动芯片的所有模块共同完成了面板发光的过程。

系统接口包括 8/9/16/18/24 位高速并行 RGB 接口,串行外部设备接口 SPI,以及高速串列接口 MIPI。从处理器过来的控制信号经过输入/输出接口向驱动芯片输入图像数据,使能信号以及时钟信号。

时序控制模块包括时序控制、数据处理以及栅源驱动控制模块和电源管理控制模块等。作用是产生源极,栅极驱动电路和芯片内部其他模块工作所需的所有时序信号。

电源管理模块主要由带隙基准, LDO 电路, 电荷泵电路和寄存器电路组成。该部分由外部电路供电,向内部各模块稳定的输入多种控制信号。例如向后级缓冲器提供基准电压,向偏置模块提供输入电流,为数字逻辑模块提供开关电压,后级所需的电源电压,伽马电路的输入电压,像素电路开关管的栅极控制电压。外部信号输入芯片后,使得电源管理模块产生不同的电压,使得各功能模块正常工作。同时数字信号控制时序模块输出各种控制信息,再通过伽马校正电路和源级驱动电路输出灰阶电压进入像素电路,控制屏幕上的色彩变化。

源极驱动电路输出的控制信号由数字模块负责提供。而为了减少结构复杂性,提升反应速度,源极驱动电路通过数模转换的方式,把外部时序电路输入的数字信号转化为模拟电压信号。作为输入信号加到像素电路驱动管的偏置端,当电路导通的时候,在 TFT 管中产生驱动电流,注入二极管,使得发光材料发光。

栅极驱动电路的主要功能是负责输出像素电路中开关管栅极上的控制电压。控制电压由数字电路提供,该电压决定了像素电路的导通和截止,所以栅极驱动电路事实上起开关而非偏置作用。因此栅极驱动电路通常是较多的通道对应一个驱动电路,所需的驱动电路数量较少,可以集成在 TFT 基板上,这种技术也被称为 GIP 或 GOA 技术。由于栅极驱动电路使用数字控制,所以需要明确开启和关断电压的具体数值,这是由电源管理模块提供的。

伽马校正电路的功能是通过控制电路调节灰阶电压的大小以改变灰阶电压曲线,使其更加贴合人眼所能感受到的亮度。让屏幕的颜色发生变化的时候显得更加柔和,色差能够有一个平滑的过渡。在该电路中,灰阶电压曲线被分成多段,每段由寄存器控制。外部数字信号输入,通过控制寄存器,把灰阶电压曲线调整成需要的形态。一般来说,灰阶电压曲线往往被分成 8 位也就是 256 个灰阶电压,通过调节电阻串中分配到的阻值大小来分配电压。而本文中使用的是红绿蓝三色电路独立发光的模式。因此,256 种灰阶电压通过恰当的排列组合可以产生超过 1600 万种色彩。当使用非线性数据结合线性 DAC 的方式进行调节时,可以采用数字电路实现。在显示屏所需的灰阶—电压曲线上选取关键节点,关键节点的电压值可通过查表从线性 DAC 的输出电压中得到,通过寄存器值的调整可实

现伽马曲线的灵活调整以适应不同的屏幕需求。

振荡器 OSC 是芯片内部所有模块所需的时钟信号的产生模块。通过时钟信号产生电路的分频、调整占空比等操作后取得行列驱动、电荷泵等模块各自所需的时钟信号后输入到各个模块中。

## 3.2 伽马校正的原理及方案

### 3.2.1 伽马校正原理

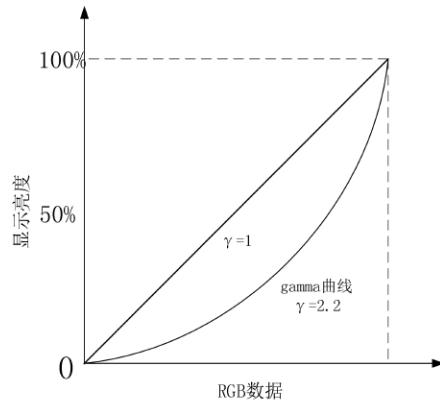

伽马校正曲线是一条反映电压与亮度关系的曲线，是一条非线性的曲线。如图 3.2 所示。如何对这条曲线进行调节，使其更适应人眼的感知需求，是本方案的重要任务。

伽马校正是已经在摄影，视频制作以及图像后期处理等方面得到广泛运用的一种技术，是一项使得图像尽可能还原其本质色彩的技术。该概念起源于 CRT 时代，屏幕中的显示亮度会被量化，与像素值一一对应。随着像素值的变化，像素电路发出的亮度发生从黑色到白色的变化，取值由 0 到 1，这些数值是被输入到显示器里的值。而由于材料与工艺的限制，CRT 显示器的亮度值和像素值之间并不是成线性关系，其关系大致为  $Y = X^\gamma$ 。Y 表示显示器件的亮度，X 表示输入的像素值，幂值  $\gamma$  为伽马值，伽马值一般情况下处于 2.2 到 2.5 的区间之中。该曲线被称为伽马曲线，伽马曲线作为比较特别的反映颜色变化的曲线。当  $\gamma$  等于 1 的时候，曲线为与横坐标轴成 45° 的直线。这表明输入信号与输出之间成线性关系，亮度与像素在数值上成线性关系。而当  $\gamma$  不等于 1 的时候，二者关系不为线性增减，造成显示效果的失真。

对于一个  $\gamma = 2.2$  的显示器件，没有经过伽马校正时它的显示效果大致相当于图中  $\gamma = 2.2$  曲线的形状。对像素电路进行伽马校正的目的就是使得显示面板出现图像的色彩能够无限趋近于其在人眼视网膜上产生的真实色彩<sup>[28]</sup>。简而言之，即人为的控制灰阶电压的大小对曲线进行调整，靠近  $\gamma = 1$  时候的理想伽马曲线，使屏幕的显示效果更加平滑。

图 3.2 显示器件输出特性

Fig 3.2 Output characteristics of display device

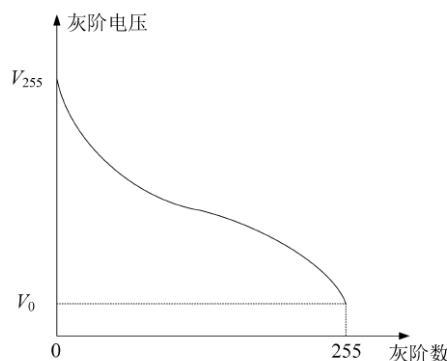

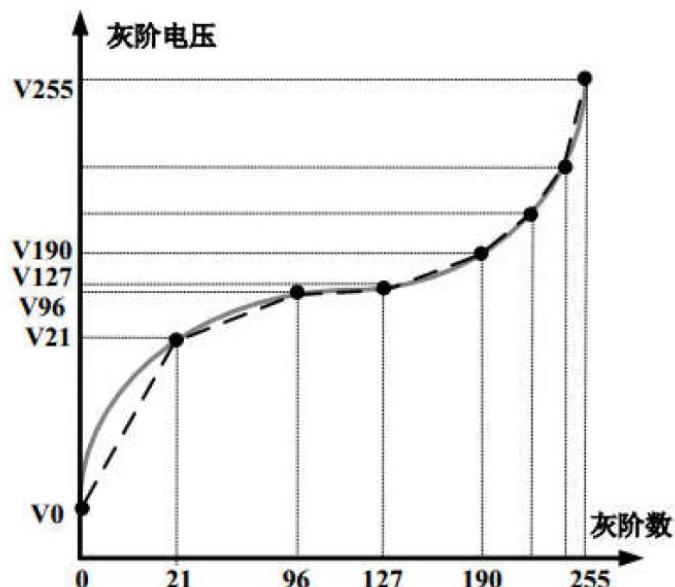

无论是 LCD 还是 OLED 显示器件的发光原理都是相似的，电压亮度曲线始终受控于外界施加的偏置电压和流过二极管的电流。而这两条曲线的增减并不是成线性关系的，因此当其中的电压电流曲线受控均匀升降的时候，屏幕的亮度会发生突变影响显示质量。同时，在不同的光照强度下人眼视网膜对色彩变化的识别能力也是不同的，视网膜在较暗的环境下对亮度变化感知能力更强。此时能够通过伽马校正的方式改变灰阶电压曲线，人为制造非线性曲线来完成理想状态的  $\gamma = 1$  的效果。图 3.3 是某一块 AMOLED 面板产生的灰阶电压曲线，显示精度为 8 位，可以产生 256 种灰阶电压。伽马校正的作用是完成显示数据到灰阶电压的非线性调整以方便调节视网膜能感知亮度能够与数字电路调控下的电压成线性关系。

图 3.3 屏幕所需的灰阶一电压曲线

Fig 3.3 Grayscale-voltage curves required for screen

### 3.2.2 本文的伽马校正优化方案

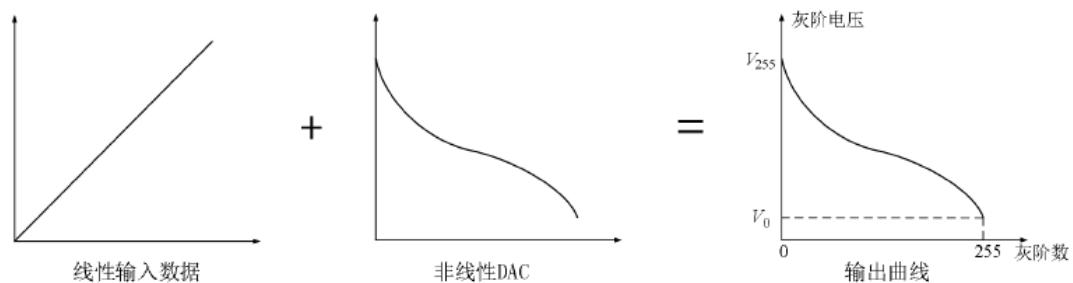

当前主流的伽马校正方案主要有两个方向。第一种是在图像数据端的，对显示数据的转换过程进行控制从而达到控制曲线，第二种是通过 DAC 来调节灰阶电压曲线以控制曲线<sup>[29][30]</sup>。国内外已经对这种技术展开了相对深入的研究，衍生出了大量的成熟理论。本文采取的是通过 DAC 来控制灰阶电压曲线的方法。这种方法也分两类，一种是线性数据结合非线性 DAC 的方式<sup>[31-33]</sup>，另外一种是非线性数据结合线性 DAC 的方法<sup>[34-36]</sup>。如图 3.4，图中显示的是线性数据结合非线性 DAC 的方法。这种情况下由前级生成的显示数据不会经过任何调控，直接输入 DAC 电路产生灰阶电压输出到像素电路。这种方法的缺点是只能对图像的显示质量做出模糊的把控，色彩失真比较严重且颜色的突变较多。而且非线性 DAC 的结构也很复杂。为了产生非线性效果，往往需要使用大量阻值各不相同的电阻来实现，这会过度挤占芯片内部空间带来体积和功耗超标的问题。为了使得生成的灰阶电压曲线尽量精确，电阻的阻值精度要求会上升。而且生成的灰阶电压的大小取决于电阻之间的比值，这对加工难度又提出了更进一步的要求。每一种非线性 DAC 只能适配一种规格的显示面板，一旦面板的参数改变，则非线性 DAC 就需要重新设计以适配新的亮度曲线，这无疑会带来成本的失控和大量的浪费。

图 3.4 线性数据结合非线性 DAC

Fig 3.4 Linear data combined with nonlinear DAC

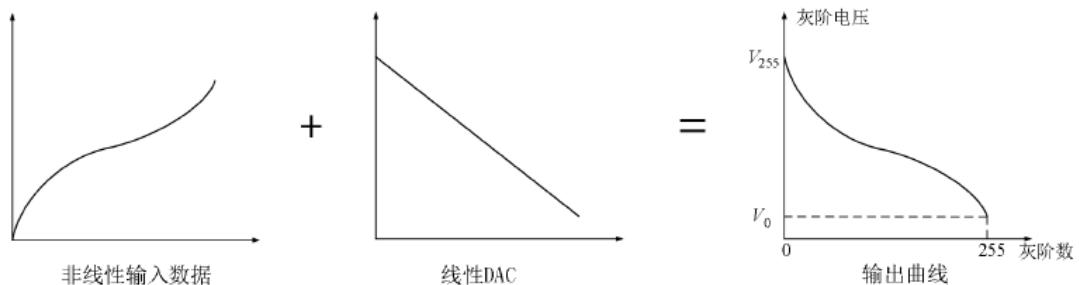

图 3.5 非线性数据结合线性 DAC

Fig 3.5 Nonlinear data combined with linear DAC

图 3.5 采用的就是非线性数据结合线性 DAC 的方法来输出灰阶电压。前级电路提供的显示数据首先被转换成成非线性的数据，再与线性 DAC 结合，产生灰阶电压。经过转换过后的显示数据不再需要保持原本的精度，通过线性 DAC 可以输出更高精度的图像，起到了提高分辨率优化显示质量的作用。与线性数据结合非线性 DAC 的方式相比，采取了线性输出方式的 DAC 不需要根据灰阶电压的大小来按比例分配电阻串的阻值，只需要大小均等的电阻即可实现。因此这种方法大大降低了工艺难度降低了成本。此外，由于电阻的需求总量上的减少，芯片的空间和功耗也可以得到大幅度的缩减，契合了设备发展的主流趋势。表中为两种伽马校正方案的综合比较。

表 3.1 伽马校正方案对比

Tab 3.1 Comparison of Gamma correction schemes

|         | 线性数据+非线性 DAC | 非线性数据+线性 DAC |

|---------|--------------|--------------|

| 数据变换    | 不需要          | 需要           |

| DAC 结构  | 复杂           | 简单           |

| 电阻匹配性   | 较差           | 较好           |

| 伽马校正分辨率 | 取决于数据位宽      | 不受数据位宽限制     |

| 灰阶电压精度  | 低            | 高            |

| 芯片面积    | 大            | 小            |

综上可得，采用非线性数据结合线性 DAC 的伽马校正方案的芯片具有高精度，低成本，低功耗，泛用性强的优点。本文即是使用非线性数据结合线性 DAC 的方案来完成伽马校正工作的。

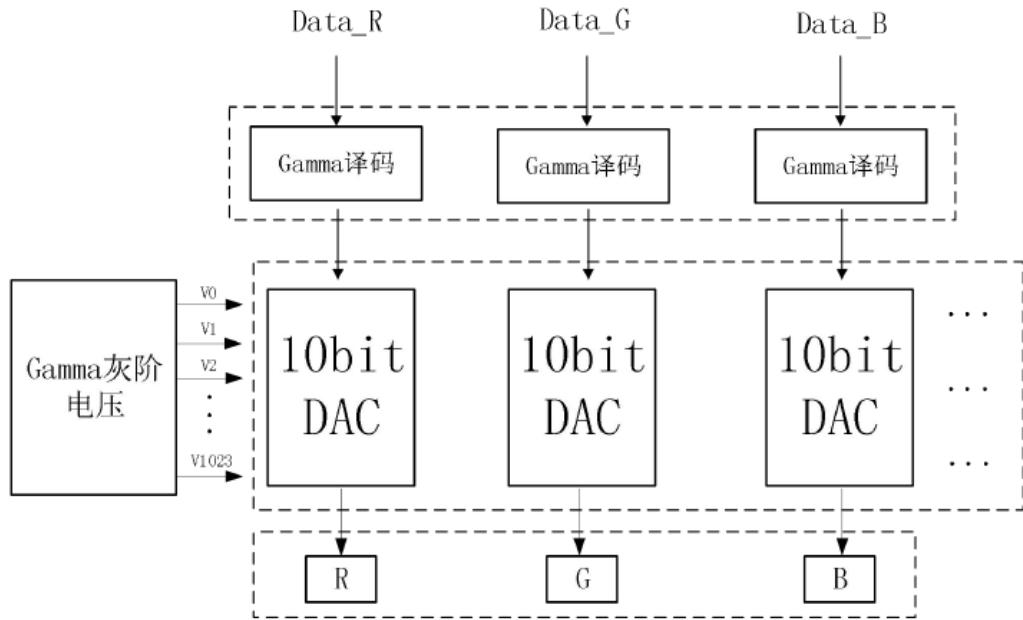

显示面板的主要设计思路即是把作为显示基本单元的完整像素点由三种次级像素红绿蓝组合而成，而这三种像素电路的伽马曲线各自有着很大的差异。如果直接用 DAC 输出灰阶电压，则会需要准备三套不同的 DAC 来分别控制三种像素发光。这大大增加了系统的复杂性浪费了芯片内部空间，而且也不符合低功耗的要求。如果使用非线性数据结合线性 DAC 的伽马校正方案，则只需要对三者差异较小的灰阶电压特征曲线进行调节。这样只需要准备一套 DAC 就可以通用于三种像素电路。具体的控制流程如图 3.6 所示。

图 3.6 R/G/B 像元校正

Fig 3.6 R/G/B pixel correction

从伽马校正电路输出的 10 位电压控制信号可以覆盖整个灰阶电压曲线并确保足够的精度。由于电压大小与色彩呈线性关系，通过数字电路的调节即可利用同一种 DAC 实现三种像素电路的分别控制。大大降低了所需的芯片面积减小了功耗和体积，有利于轻量化的设计。

对于大部分显示面板来说理想的灰阶电压之间的对应关系是非线性的，而线性 DAC 的输出曲线显然无法与之一一对应。电压对亮度的调节能力存在差别的结果必然是显示亮度发生突变从而图像失真。本文的方案则是利用输入的图像数据曲线与 DAC 的结合，达成显示亮度曲线与电压曲线的同步效果，以实现进一步提升灰阶电压精度的效果。

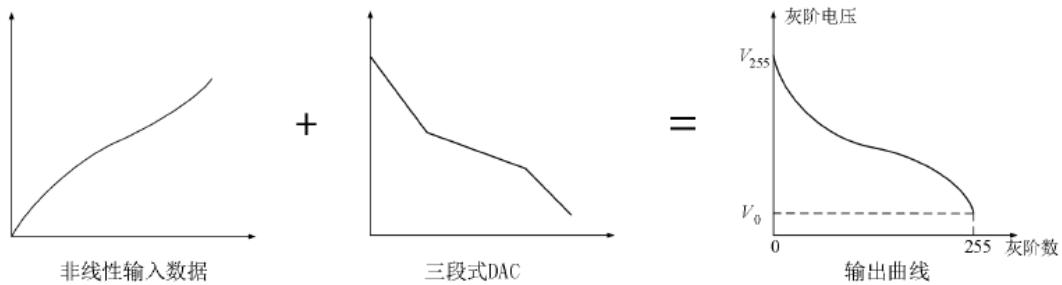

DAC 的输出曲线与亮度曲线的重合度越高，则 DAC 对显示色彩的控制能力越精确，显示效果就越好。本文采用分段法处理灰阶电压曲线，每一小段分得越细与亮度曲线的重合度就越高，控制也就越精细。然而与此同时分段分得越多意味着 DAC 所需要利用的位宽越大，电阻的需求量也就越多。同时为了驱动负载和保证输出电压的稳定性，芯片内部也不得不增加更多的缓冲器。位宽越高，占用的芯片面积就越大，随之而来的是功耗的快速上升和成本的增加。

图 3.7 本文提出的伽马校正方案

Fig 3.7 Gamma correction scheme proposed in this paper

在对调节精度和功耗成本做出平衡后，本文选择将 DAC 输出曲线分为三段。从图 3.7 中可以看出，把曲线分为三段大致上能够反映亮度随人眼感知变化的趋势。如此只需要较小的位宽就可以使得灰阶电压曲线更为接近目标曲线，大大简化的 DAC 的结构，节约了芯片的内部空间。

使用线性 DAC 的另外一大优点在于最终输出到像素电路的显示数据不受初始图像数据精度的影响，提升 DAC 的位宽，是可以做到优化显示效果的。本文采用的是位宽为 10 位的 DAC，其输出电压的精度可以达到  $2.1\text{mV}$ 。在相同结构下对邻近位宽的 DAC 的性能测试可以发现，9 位 DAC 下输出电压的精度为  $4.3\text{mV}$ ，与设计指标规定的  $3\text{mV}$  精度有了不小的差距。而当位宽提升到 11 位的时候，输出电压的精度仅提高到了  $1.1\text{mV}$ ，但付出了更多的芯片面积和功耗作为代价。因而 10 位的线性 DAC 为此设计的最优解。

### 3.3 伽马校正电路的系统设计

#### 3.3.1 伽马校正电路的架构

在显示驱动芯片中，伽马校正的输出是给源级驱动电路提供前级的灰阶电压。各模块的连接关系如图 3.8 所示，红色线框部分是伽马校正电路，其它模块属于源级驱动电路。从图 3.8 中可看出，伽马校正电路主要包含伽马校正主体电路 (Main Gamma correction circuit)、数据转换 (Data Converter)、微调寄存器 (Fine Adjustment Register)、线性 DAC 这四个模块。

图 3.8 伽马校正电路架构

Fig 3.8 Structure of Gamma correction circuit

数据转换部分的作用是实现线性图像数据到驱动数据的非线性变换,将输入 8 位图像数据转换为 10 位驱动数据。

伽马校正主体电路、微调寄存器的作用是确定伽马曲线上的关键灰阶电压,即实现幅度调节、斜率调节和微调节三个过程。关键灰阶电压共为 26 个,由于 R/G/B 三色的伽马曲线不一样,所以,微调寄存器共需要 78 个。

线性 DAC 的作用是把数字信号转化为灰阶电压,采用两级线性 DAC 级连结构来实现 10 位 DAC,第一、二级分别为 6 位和 4 位。

伽马校正主体电路负责为第一级 DAC 提供 65 个灰阶电压。6 个伽马校正电压在寄存器的控制下平均分布在伽马曲线上,分别调节每一部分的斜率和弧度。灰阶电压与亮度在数值上成一一对应关系,例如当设计位宽为 6bit 时,总共可以产生 64 个亮度梯度。这样灰阶电压和亮度梯度之间就形成了可供量化的关系,产生了伽马曲线。因此,能够保证输出电压的平稳,有较快的响应速度使得像素电路能够迅速建立灰阶电压,就是非常关键的设计指标了。

把图像转化为电压的方法有查找表法与数学算法两种,查找表法是将前级电路传输而来的图像数据转化为数字信号并送至寄存器储存。而后源级驱动模块利用图像数据与色彩的一一对应分配相应的灰阶电压,从而得出灰阶电压曲线。在实际操作过程中因为有提高精度的需求,图像数据的位宽往往比 DAC 的位宽小,所以转化过程会用到很多寄存器,占用过多的芯片内部空间。所以实际上往往算法的使用频率比较高。

本文中所使用的的算法是通过将灰阶电压曲线分为不同的部分分别处理的。

先按照既定需求把灰阶电压曲线分为 32 个小节，每个节点的电压都被转化为数字信号存储在寄存器当中。剩下的数据则被分布在这 31 个电压之间的小段上，由线性插值法计算得出。这样就大大减少了寄存器的需求量，节约了芯片内部空间。

### 3.3.2 伽马校正主体电路的系统设计

输入图像数据的转换是由数字部分来完成，灰阶电压的产生则是由数模混合电路来产生，包括关键灰阶电压产生和线性 DAC。

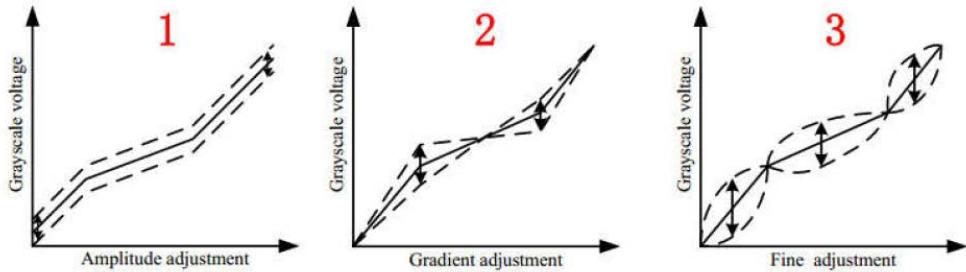

由于硬件结构的限制，一般情况下，非线性曲线是通过对该曲线进行分段线性化来实现的，如图 3.9 所示。首先确定非线性曲线上关键点，然后将每两个相邻关键点用直线连起来，其它点通过对相邻关键点之间进行插值得到，从而做到拟合非线性曲线。

图 3.9 灰阶电压曲线的分段线性化

Fig 3.9 the piecewise linearization of Grayscale-voltage curves

因此，确定非线性曲线上的关键点是非常重要的。图像数据和灰阶电压之间的非线性关系也是通过分段线性化来实现，其实现过程如图 3.10 所示，主要包含以下三个步骤：

- (1) 确定非线性曲线上的最低点和最高点，一般称为幅度调节。

- (2) 确定曲线两个中间点，从而将曲线分成三段，一般称为斜率调节。

- (3) 确定曲线上的关键点，一般称为微调。

图 3.10 关键灰阶电压产生过程

Fig 3.10 the generation procedure of key grayscale voltage

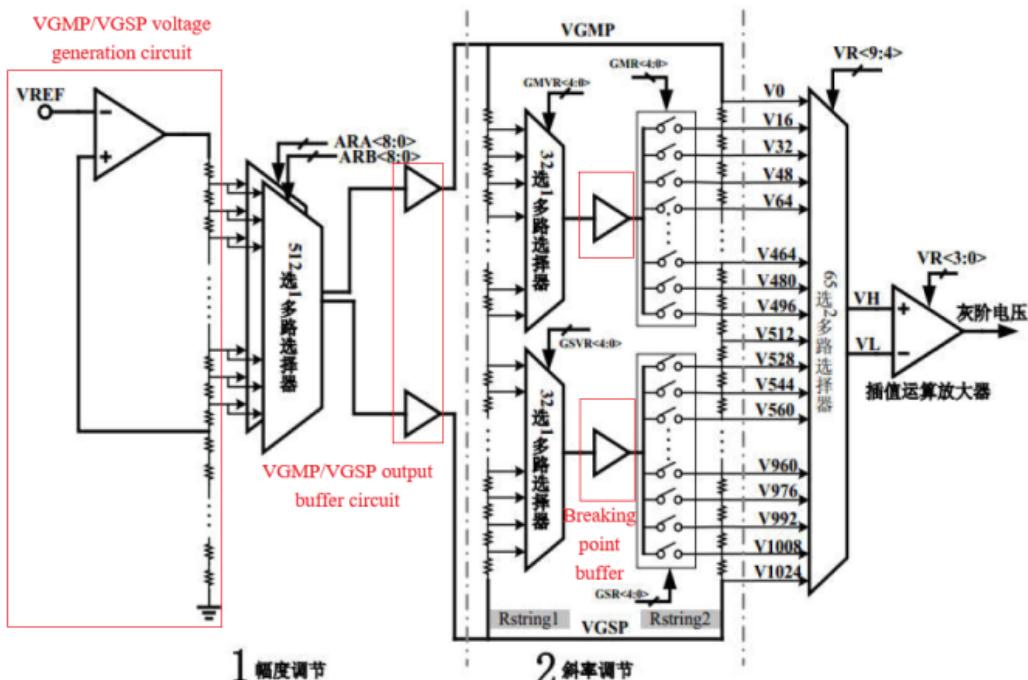

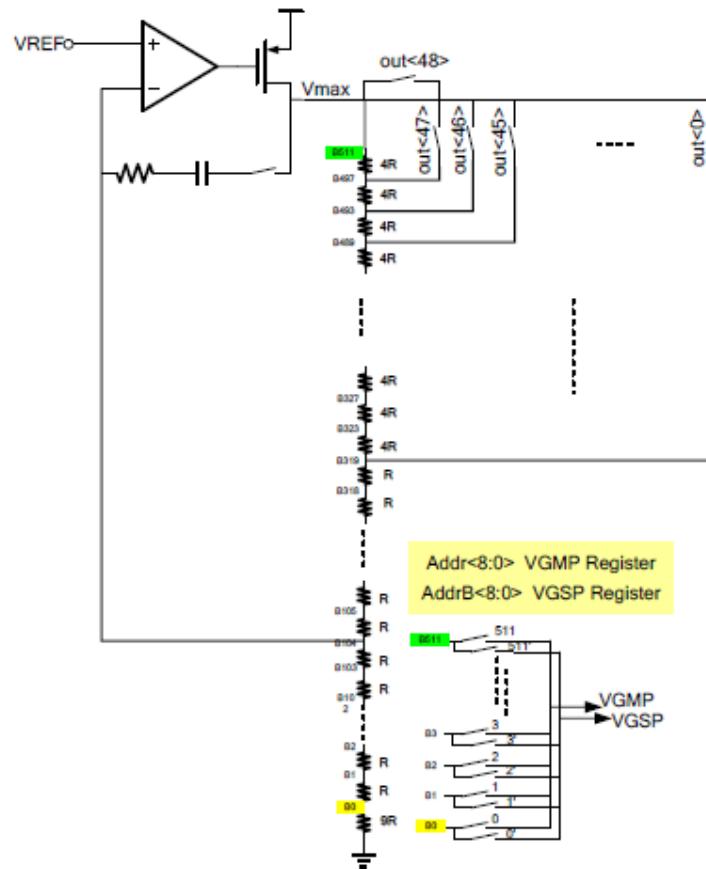

对于伽马曲线来说，无论是采用线性 DAC 还是非线性 DAC 来实现数据到电信号的转换，最终都是实现一条数模转换的非线性曲线。从前面的论述可知，要实现伽马曲线，首先要确定关键灰阶电压，然后对每两个关键灰阶电压之间进行插值得到所有的灰阶电压。图 3.11 中的是伽马校正主体电路的整体结构，包括 VGMP/VGSP 电压产生电路，512 选 1 多路选择器，VGMP/VGSP 输出缓冲器电路，电阻串 Rstring1，32 选 1 多路选择器和拐点与输出缓冲器电路。

图 3.11 伽马校正主体电路结构

Fig 3.11 main structure of GAMMA correction circuit

从图 3.11 中电路可以看出，由前级的 VREF 产生电路产生大小为 1.4V 的参考电压输入后级的 VGMP/VGSP 产生电路。这个 LDO 的主要功能是为了给由 ARA<8:0>和 ARB<8:0>控制的 512 选 1 的多路选择电路提供电流输出，以产生幅度调节所需的最高电压 VGMP 和最低电压 VGSP。输出的电压通过两个缓冲器，将

选择出来的 VGMP/VGSP 电压输出到电阻串的两端。输出电压进入斜率调节单元，分成高斜率调节节点 VH 和低斜率调节节点 VL。斜率调节的主要目的是将伽马曲线分成三段斜率不同的直线来确定曲线的基本趋势。本文通过采用两个电阻串 Rstring1、Rstring2 来实现斜率调节，每个电阻串的个数为 64。电阻串 Rstring1 用来产生三段曲线的两个分界点处所需要的电压值，电压值的大小通过改变斜率寄存器 GMVR<4:0>、GSVR<4:0>的值来确定，电阻串 Rstring2 不仅决定了伽马曲线三段的斜率，而且代表了灰阶数，实现数据到电压的转换。电阻串 Rstring1 产生两个分界点的电压值 VH 和 VL 通过控制寄存器 GMR<4:0>、GSR<4:0>来调节插入点的位置。之后通过拐点缓冲器，以及另一个 32 选 1 的选择器将 VH 的电压值输出到电阻串 Rstring2 的某一位置，从而改变电阻串 Rstring2 上的电压曲线，VL 同理。此时电阻串 Rstring2 上的电压即为目标伽马曲线，根据最终屏幕所需灰阶电压曲线，结合三段式 DAC，确定 10bit 数据和 8bit 数据之间的对应关系，完成非线性数据的转化。源极驱动电路根据转换后的 10bit 数据产生对应的电压值驱动像素电路，完成灰阶电压的产生。

根据上面的工作流程可以发现，VGMP/VGSP 电压产生电路作为 LDO 需要在尽可能低的电源电压下输出 VGMP 和 VGSP 两个差值很大的电压输出，这就意味着需要数量较多的电阻完成分压。虽然输出电压靠的是电阻的比例关系输出，只要每个电阻的匹配度足够高就足以保证输出精度。但对于产生幅度调节电压的 LDO 电路来说，电阻串产生的误差将导致 VGMP/VGSP 电压的建立出现问题。最终误差将传导到后级所有的灰阶电压上，对显示精度产生巨大影响。因而该电路不但有精度方面的要求，还需要使用不同的电阻工艺角对电路仿真验证，以证明电阻误差是在允许的范围内。对于 VGMP/VGSP 输出缓冲器电路，不仅需要同时驱动 Rstring1 和 Rstring2 的电阻串，作为灰阶电压曲线中的最高点电压和最低点电压，同样需要保证输出精度。由于其共模输入范围摆幅较大，则需要强化其负载驱动能力以及保证不同工作条件下跨导的一致性。对于伽马拐点与输出缓冲器电路来说，它需要适应像素电路在 60Hz 的刷新率下快速完成灰阶电压的建立，这对于缓冲器电路的速度产生了极高的要求，高速度意味着高负载电流。同时，随着显示的精度越来越高，灰阶电压节点的划分也就越来越细致，因而缓冲器的精度需求也就越来越高。同样的，灰阶电压节点数量急速上升带来的就是缓冲器数量的增加，此时就需要压缩单个缓冲器的芯片面积和功耗。

### 3.4 伽马校正电路的设计指标

#### 3.4.1 系统指标需求

本论文设计的伽马校正电路适用于最大分辨率为 1080\*2220，最高 1670 万色的 AMOLED 显示面板，同时支持 262K 色以及 65K 色的伪彩色和 8 色的待机模式。表 3.2 是本文所设计的驱动芯片伽马校正电路适用的参数要求。

表 3.2 伽马校正整体设计指标

Tab 3.2 Global index of Gamma correction circuit

| 参数      | 最小值                         | 典型值  | 最大值 | 单位              |

|---------|-----------------------------|------|-----|-----------------|

| 电源电压    | 4.5                         | 5.5  | 6.5 | V               |

| 灰阶数     | 同时支持 3 色 RGB 像素 256 灰阶的伽马曲线 |      |     |                 |

| 输入/输出电压 | 0/0.2                       |      | 6.3 | V               |

| 电压精度    |                             | 3.5  |     | mV              |

| 温度补偿系数  |                             | 11   |     | mV/°C           |

| 响应时间    |                             | 50   |     | us              |

| 静态电流    |                             | 1.6  |     | mA              |

| 关断电流    |                             | 0.04 |     | uA              |

| 功耗      |                             | 8.8  |     | mW              |

| 面积      |                             | 0.4  |     | mm <sup>2</sup> |

#### 3.4.2 伽马校正电路关键模块的设计指标

##### 1. VGMP/VGSP 产生电路的设计指标

VGMP/VGSP 产生电路主要是产生伽马曲线所需要的幅度电压，且为后级电路 VGMP、VGSP 输出缓冲器电路提供参考电压。则要求输入端有足够的共模输入范围，较小的静态电流，同时还需要考虑电压精度以及建立时间等指标。综上，VREF 产生电路的设计指标如表 3.3 所示。

表 3.3 VGMP/VGSP 产生电路的设计指标

Tab 3.3 Design index of VGMP/VGSP offering circuit

| 指标     | 典型值     | 单位 |

|--------|---------|----|

| 输入电压范围 | 1.4     | V  |

| 输出电压范围 | 0.2~6.3 | V  |

| 建立时间   | 20      | us |

|           |        |        |

|-----------|--------|--------|

| PSRR      | 30/25  | dB/KHz |

|           | 28/100 | dB/KHz |

| 环路增益/相位裕度 | 60/60  | dB/°   |

## 2. VGMP/VGSP 输出缓冲器电路的设计指标

VGMP 和 VGSP 输出缓冲器主要是提高幅度高电压 VGMP 和幅度低电压 VGSP 的驱动能力, 该部分电路需要在较大的输入电压摆幅下保持输出的稳定性, 以及较快的反应速度, 精度方面的要求也需要得到考虑。表 3.4 为该部分电路的设计指标。

表 3.4 VGMP/VGSP 缓冲器电路的设计指标

Tab 3.4 Design index of VGMP/VGSP buffer circuit

| 指标        | 典型值     | 单位     |

|-----------|---------|--------|

| 输入电压范围    | 0.2~6.3 | V      |

| 输出电压范围    | 0.2~6.3 | V      |

| 建立时间      | 3       | us     |

| PSRR      | 40/25   | dB/KHz |

|           | 30/100  | dB/KHz |

| 环路增益/相位裕度 | 60/60   | dB/°   |

| 负载电流      | 800     | uA     |

## 3. 伽马拐点与输出缓冲器的设计指标

该部分缓冲器需要驱动 15 个斜率调节点的输出电压, 因此其静态电流需要尽可能的小, 输出电压精度要尽可能的高, 同时芯片面积及响应时间也需要得到兼顾。表 3.5 为伽马拐点与输出缓冲器的设计指标。

表 3.5 伽马拐点与输出缓冲器的设计指标

Tab 3.5 Design index of GAMMA breaking point output buffer

| 指标        | 典型值     | 单位     |

|-----------|---------|--------|

| 输入电压范围    | 0.2~6.3 | V      |

| 输出电压范围    | 0.2~6.3 | V      |

| 建立时间      | 5       | us     |

| PSRR      | 60/0    | dB/KHz |

|           | 40/1.6  | dB/KHz |

| 环路增益/相位裕度 | 65/60   | dB/°   |

### 3.5 本章小结

本章对 AMOLED 显示驱动芯片的整体系统做了简要介绍，并详细分析伽马校正的原理和校正方案，设计优化的伽马校正方案。在此基础上，确定了伽马校正的系统结构和系统设计指标，以及各关键模块的设计指标，包括 VGMP/VGSP 产生电路、VGMP/VGSP 输出缓冲器电路以及伽马拐点与输出缓冲器等。

## 第四章 伽马校正电路的设计与仿真

### 4.1 VGMP/VGSP 电压产生电路

#### 4.1.1 VGMP/VGSP 电压产生电路的设计

芯片中 LDO 电路的全称叫做低压差线性稳压器电路。在该电路中，LDO 电路的主要作用是形成提供稳定，精确的输出电压。本文 VGMP/VGSP 电压产生电路的结构图如图 4.1 所示，它是一种 LDO 电路，主要目的是产生伽马曲线所需要的幅度电压，并为后级的 VGMP、VGSP 输出缓冲器电路提供参考电压。其放大器部分采用轨对轨结构，扩大了共模输入范围，输入对管正常工作的时候处于亚阈值区，起到了减小功耗的作用。

图 4.1 VGMP/VGSP 产生电路结构图

Fig 4.1 VGMP/VGSP generating circuit

从图 4.1 中的电路可以看出，VGMP、VGSP 可以分别通过 9 位寄存器调节输出，且和 VREF 之间的关系如式所示。

$$\frac{VGMP}{VGSP} = \frac{9+n}{112} VREF \quad n = 1, 2, 3 \dots 511 \quad (4.1)$$

### 4.1.2 VGMP/VGSP 电压产生电路的指标分析

LDO 电路作为伽马校正模块的最初输入级，其性能的好坏决定了后级的输入是否稳定。针对本文的设计指标，LDO 电路应该满足以下需求。

#### 1. PSRR

PSRR 是与 LDO 电路性能相关的重要设计指标，它体现了系统对输入信号中掺杂的噪声的抑制能力，这是电源电压噪声抑制系数。电源电压往往带有大量纹波，在经过 LDO 电路时可以得到大幅度的抑制，这样就可以得到所需的较为纯净的直流信号。PSRR 的公式可以表示为：

$$PSRR(dB) = 20 \log \frac{V_{ripple(in)}}{V_{ripple(out)}} \quad (4.2)$$

上面的公式说明了系统对噪声的抑制能力越强 PSRR 就越高。在该设计中，所需的 PSRR 要求大于 60dB。

#### 2. 直流增益

在闭环系统中，环路增益是一个对性能影响很大的因素。环路增益是信号在通过整个反馈电路后输出信号相对于输入信号增加的倍数。对一个稳定的闭环系统来说，增益越大，精度越高。根据设计要求，本电路中的环路增益需要在 60dB 以上。

相位裕度是衡量负反馈系统稳态的重要指标。该指标衡量在系统从启动到最终达成稳态之间，所能够承受的相位波动幅度。相位裕度与系统的稳定性成正相关。但缺点是当相位裕度过高的时候系统的响应时间被延长，整个系统的反应变得迟缓。所以设计 LDO 电路必须在速度和稳定方面做平衡，需要结合电路的具体需求找到一个可以接受的相位裕度。

#### 3. LDO 电路的瞬态响应

LDO 电路在工作过程中，会遇到输入电压和负载发生大幅度变化的过程。输入端的变化可能来源于共模输入电压较大，供电故障或温度等原因造成。输出负载则会因为数字电路控制，导致其阻值，负载电流产生剧烈的波动。这会造成 LDO 输出端电压的突变，影响整个系统的稳定性。有着良好瞬态特性的 LDO 电路可以在输入或负载发生突变的时候有效降低波动的影响，使得输出电压尽快回到设计值上去。

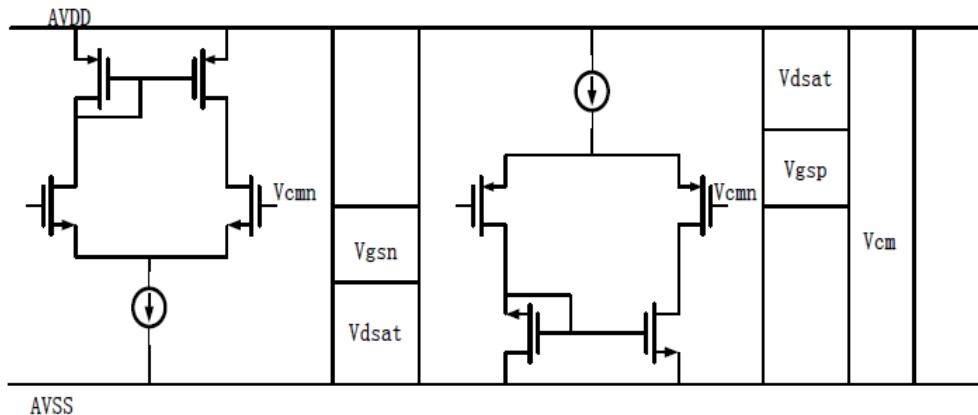

### 4.1.3 轨到轨输入级设计

由于 VGMP/VGSP 电压产生电路的输入级较大的共模输入范围。为了保证系统在这种电压变化下依然能够稳定的输出结果, 本文采用轨到轨的输入结构来解决这一问题。即使用 PMOS 与 NMOS 差分对管并联的结构而实现, 如图 4.2 所示<sup>[37-38]</sup>。

图 4.2 轨对轨输入级结构

Fig 4.2 rail-to-rail input stage

从图 4.2 中可以得出, NMOS 差分对管的工作范围:

$$V_{SS} + V_{gsn} + V_{dsat} \leq V_{cm} \leq V_{DD} \quad (4.3)$$

同理, PMOS 差分对管的共模输入范围为:

$$V_{SS} \leq V_{cnp} \leq V_{DD} - (|V_{dsat}| + |V_{gsp}|) \quad (4.4)$$

由于采用了 NMOS 和 PMOS 差分对管并联的设计, 所以共模输入范围为二者叠加:

$$V_{SS} \leq V_{cm} \leq V_{DD} \quad (4.5)$$

如此就将系统正常工作的电压范围扩展到从电源到地。

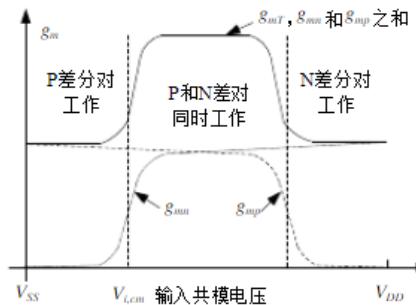

同样的, 输入级使用互补结构固然提高了共模范围, 也带来了系统总跨导的新变化。在输入电压不同的适合, 跨导总共会呈现以下几种情况。

当输入电压总体较小, 接近地电压  $V_{SS}$  的情况下, 电路中只有 PMOS 对管工作而 NMOS 对管处于关闭状态。此时的系统总跨导  $g_m$  实际上只相当于 PMOS 管的跨导  $g_{mp}$ 。当输入电压较高接近电源电压  $V_{DD}$  的时候, 只有 NMOS 差分对管工作而 PMOS 差分对管截止。这时候系统的总跨导与 NMOS 管的跨导  $g_{mn}$  相当。如果输入电压大小处于二者之间的時候, NMOS 管与 PMOS 管均处于工作状态。此时系统的总跨导  $g_m$  为 PMOS 管和 NMOS 管二者跨导的总和  $g_{mn} + g_{mp}$ 。

运算放大器电路的直流增益与系统的总跨导有关, 而 MOS 管跨导又随着输入电压的变化而变化。所以输入端等效跨导的波动势必会引起运放单位增益带宽的

变动。同时单位增益带宽的变动会造成相位裕度降低到设计指标以下，这样会造成系统稳定性下降，影响输出精度和响应速度。

由此则引入了跨导恒定的概念。在保持电路大体性能的同时寻求在输入电压波动大情况下达到较为稳定的总跨导。而跨导恒定方案通常要对电路结构做出较大幅度的改动，这种改动容易造成电路的其他性能指标发生劣化，保证了跨导的稳定势必造成在功耗、芯片面积上的取舍<sup>[39-41]</sup>。由于本文只要求 LDO 能够满足覆盖一个尽可能宽的共模输入电压的范围，使得在该前提下的增益、带宽、稳定性等都可以达到设计的预期值。因此 VGMP/VGSP 电压产生电路选择不使用跨导恒定结构。在下文中的缓冲器电路里，跨导恒定结构将发挥至关重要的作用。

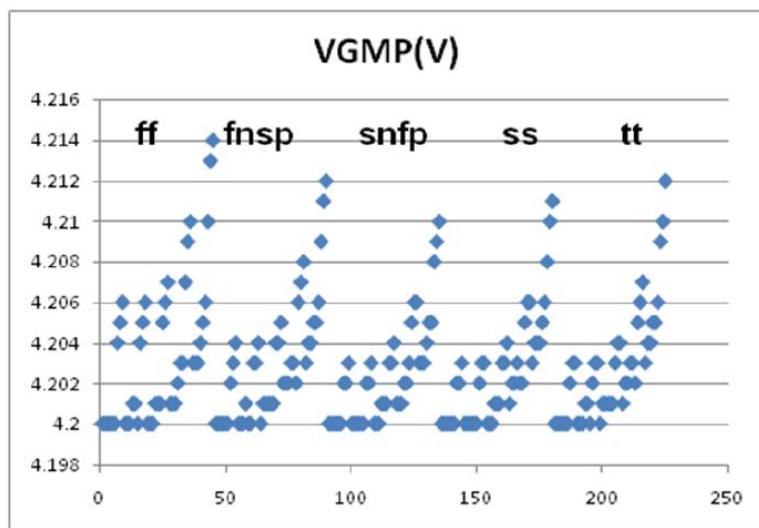

#### 4.1.4 VGMP/VGSP 电压产生电路的仿真与分析

##### (1) 直流仿真

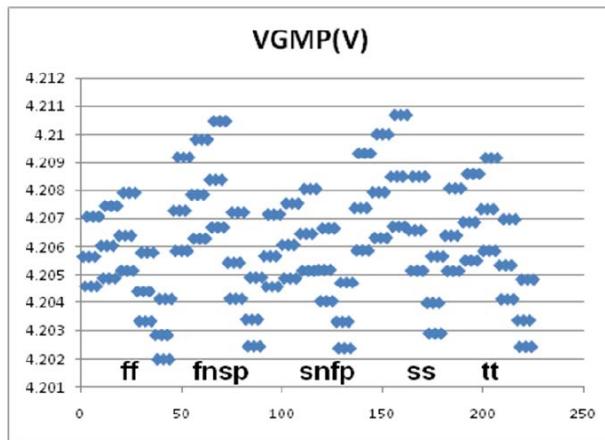

当输入参考电压  $V_{REF}=1.4V$ ，固定寄存器  $ADD<8:0>$  和  $ADD_B<8:0>$  的值，输出电压  $VGMP=4.2V$ 、 $VGSP=0.4V$  时 PVT 仿真结果分别如图 4.3，图 4.4 所示。

图 4.3 输出电压 VGMP

Fig 4.3 output voltage VGMP

图 4.4 输出电压 VGSP

Fig 4.4 output voltage VGSP

可以看出，在电路正常工作的时候，PVT 变化对输出电压 VGMP、VGSP 影响不大。

## (2) 稳定性仿真

输入参考电压  $V_{REF}=1.4V$ ，输出电压  $VGMP=4.2V$  情况下电路的稳定性仿真结果如图 4.5 所示。

(a) 环路增益

(b) 相位裕度

(c) GBW

图 4.5 VGMP/VGSP 产生电路 STB 分析

Fig 4.5 STB analysis of VGMP/VGSP Generating circuit

从仿真结果可以看出，环路增益都在 55dB 以上，相位裕度可以达到 90°，满足设计要求。

### (3) PSRR 分析

当输入参考电压  $V_{REF}=1.4V$ ，输出电压  $VGMP=4.2V$  情况下电路的 PSR 仿真结果如图 4.6 所示。

图 4.6 输出电压 VGMP 电源抑制比

Fig 4.6 Power supply rejection ratio of VGMP voltage

从仿真结果可以看出，电源抑制比在 0Hz 时不低于 40dB，低频段 25kHz 处大于 30dB，100kHz 处大于 28dB，满足设计要求。

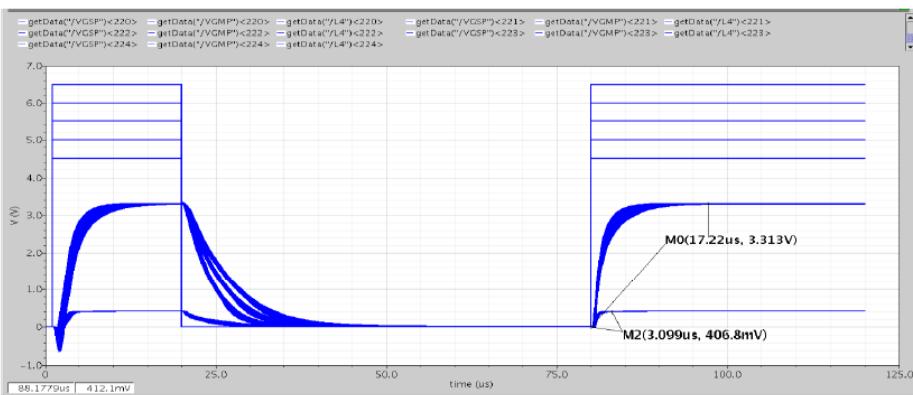

#### (4) 启动过程瞬态仿真

输入参考电压  $V_{REF}=1.4V$ ，输出电压  $VGMP=3.3$ 、 $VGSP=0.4V$  时，电路的启动过程如图 4.7 所示。

图 4.7 VGMP/VGSP 电路启动过程仿真

Fig 4.7 Start-up simulation of VGMP/VGSP circuit

由仿真结果可得，VGMP/VGSP 电路的启动时间随着输入电压的变化在

3.099us 到 17.22us 之间，符合设计指标要求。

## 4.2 VGMP/VGSP 电压输出缓冲器电路

### 4.2.1 VGMP 输出缓冲器电路设计

AMOLED 电路负载通常为几十 PF 的电容负载或几千欧的电阻负载。在电路前级驱动能力较小的情况下，需要增加缓冲器来提高灰阶电压的驱动能力，使得 VGMP/VGSP 电压产生电路的输出的灰阶电压能够快速，精准的建立在负载电阻串上。输出缓冲器作为 LDO 与灰阶电压 DAC 第一级电阻串相互衔接的部分，其输出灰阶电压的精度对图像质量有举足轻重的作用。

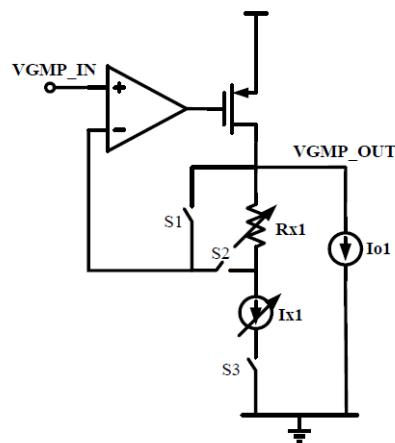

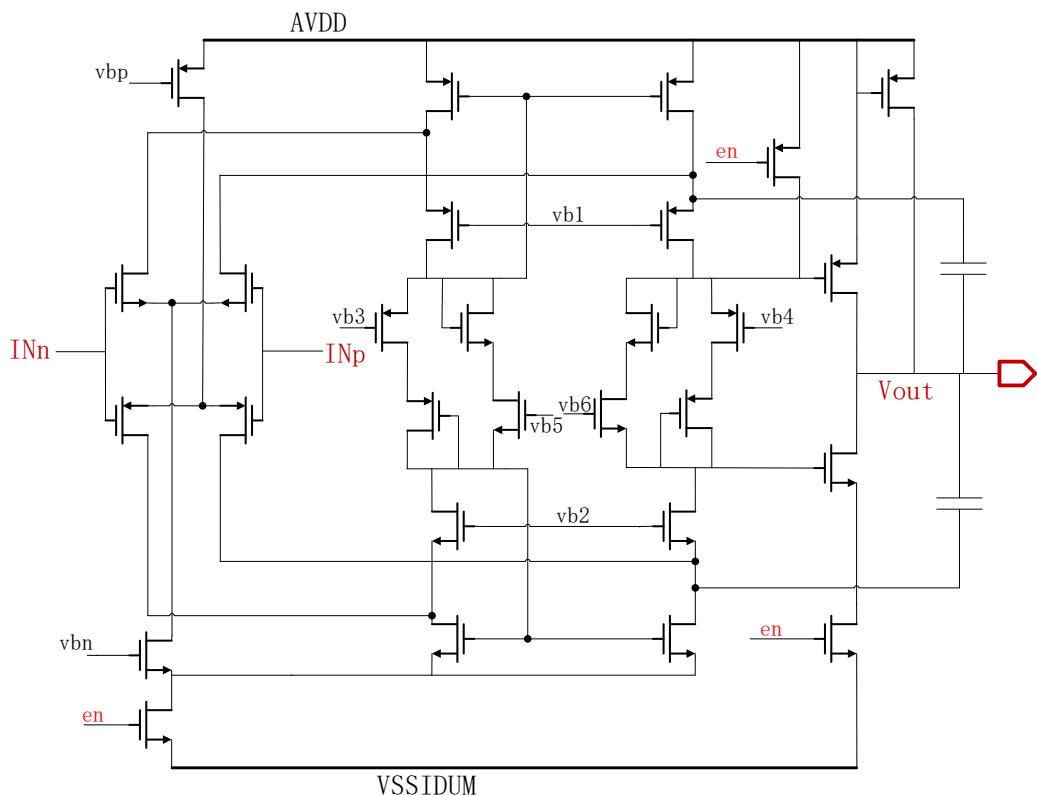

在本文中，VGMP 输出缓冲器电路主要是提高幅度高电压 VGMP 的驱动能力，电路结构如图 4.8 所示。

图 4.8 VGMP 输出缓冲器电路结构

Fig 4.8 Structure of VGMP buffer circuit

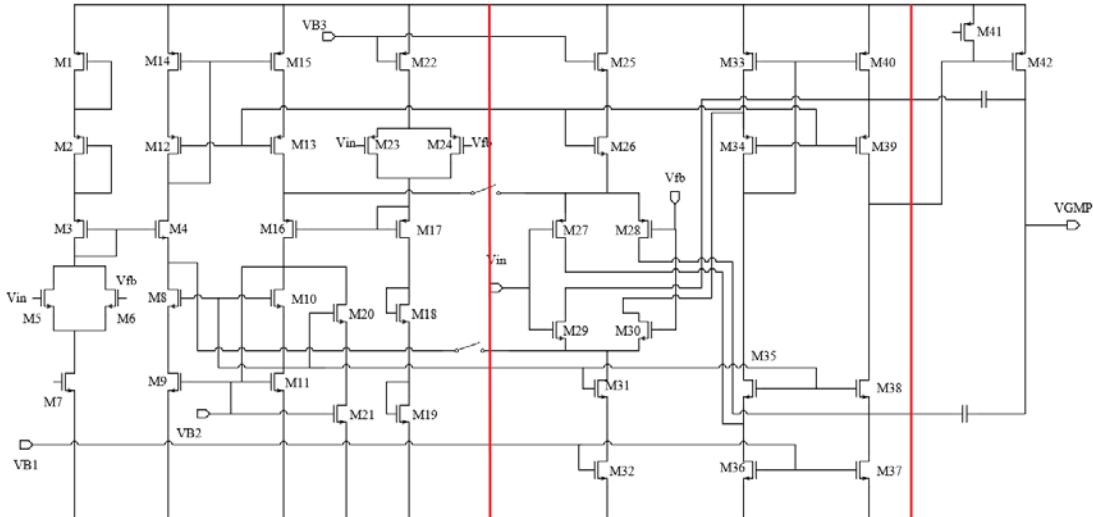

其中运算放大器部分电路的结构如图 4.9 所示。

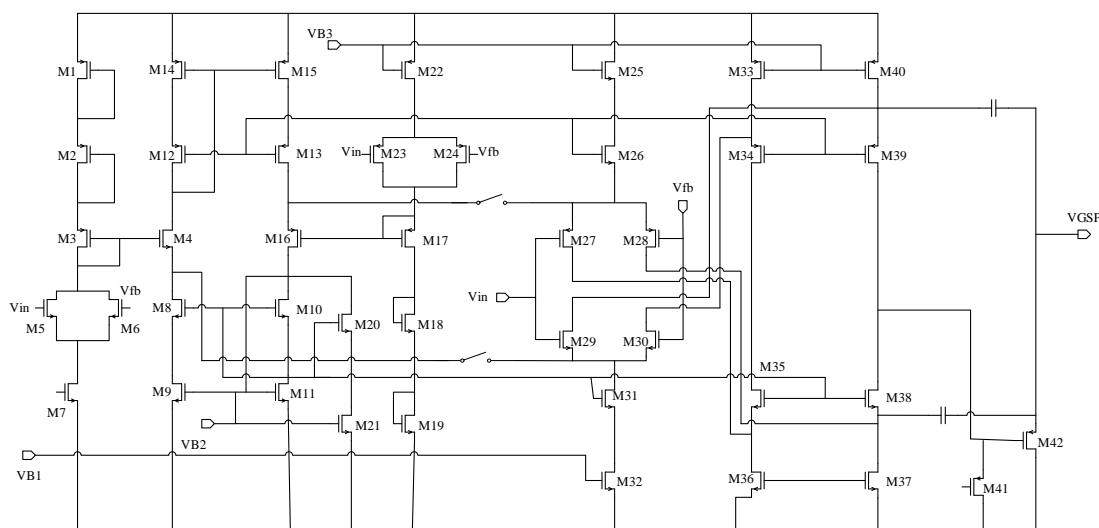

图 4.9 VGMP 输出缓冲器的运算放大器电路

Fig 4.9 operational amplifier circuit of VGMP buffer

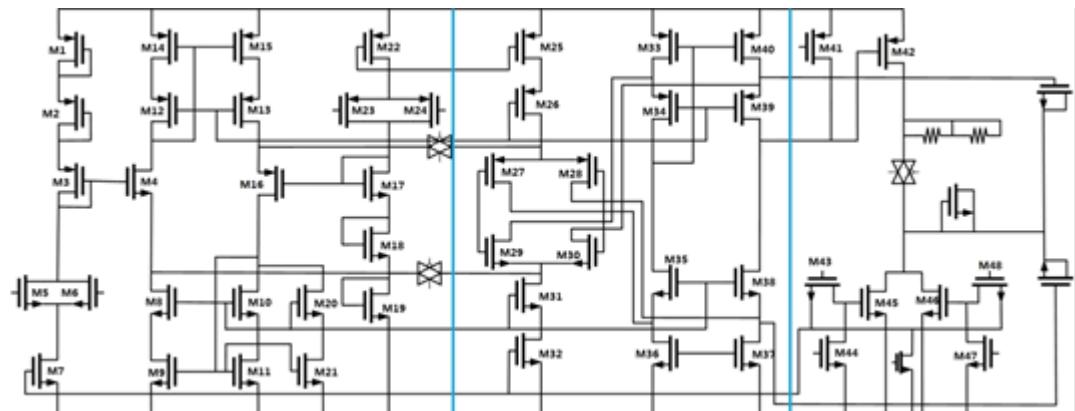

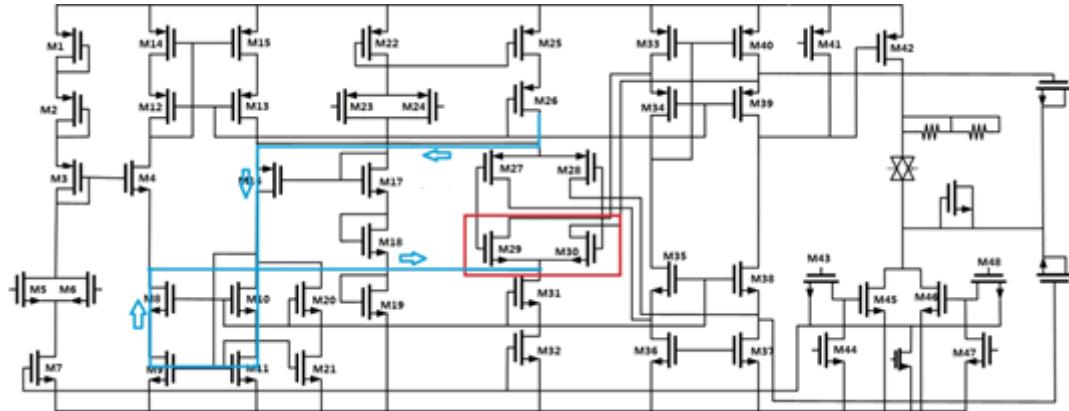

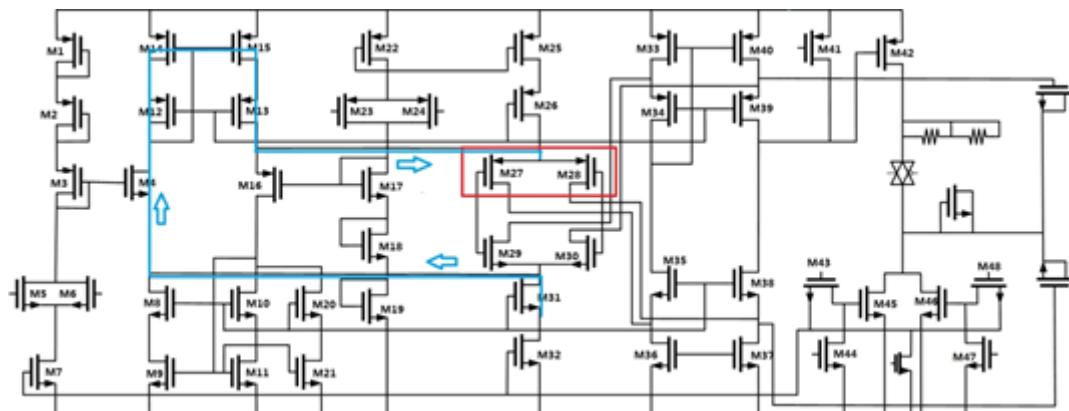

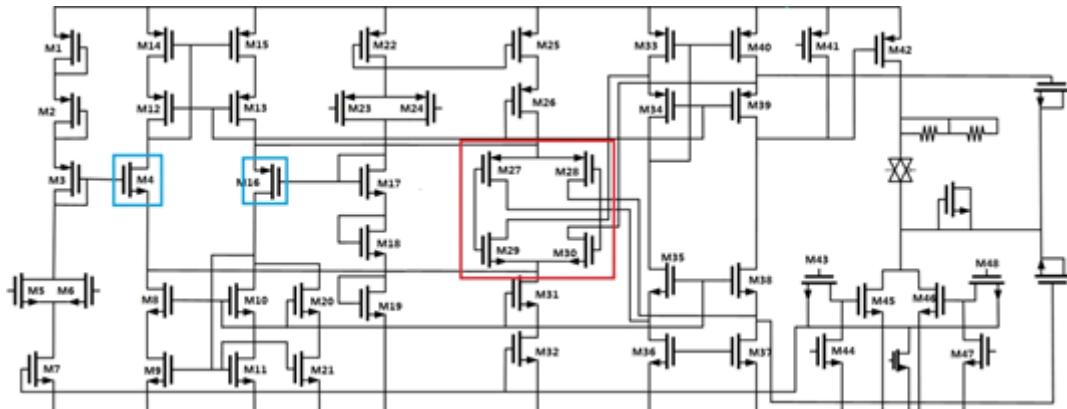

图 4.9 为 VGMP 输出缓冲器电路的主体功能模块。可以看出整个电路从左至右依次是由跨导恒定部分，放大器部分和输出部分共同构成的。其中 M5，M6 管以及 M23，M24 管为开关管，负责跨导恒定部分电路的开启和关断。M27，M28 管和 M29，M30 管为运放差分对管，其中 M27，M29 管接输入电压，M28，M29 管与输出部分相连，构成单位增益负反馈结构。同时输出部分采用 Cascode Miller 补偿，在该模式下，用更小的电容即可达到更好的补偿效果，有着更好的频率特性，使得缓冲器的工作更加稳定。该运算放大器的差分对管工作在亚阈值区，静态电流比起工作在饱和区时大幅度减少，降低了功耗。

在图 4.9 中，VGMP 输出缓冲器电路具有两种工作模式：当开关管 S1 闭合，S2、S3 打开，电路处于 Buffer 模式。当 S1 打开，S2、S3 闭合，成为具有温度补偿功能的 Buffer 模式。此时，输出电压 VGMP\_OUT 在温度上升的同时而随之提高，且结合具有温度补偿功能的 VGSP 输出缓冲器电路来实现伽马曲线的温度补偿功能。

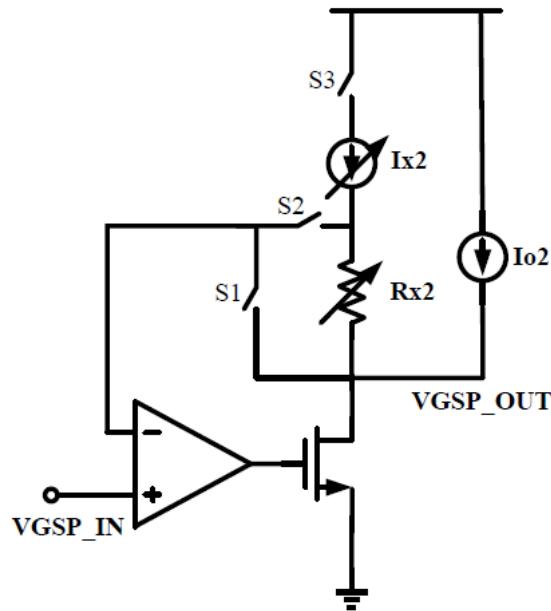

#### 4.2.2 VGSP 输出缓冲器电路设计

VGSP 输出缓冲器主要是提高幅度低电压 VGSP 的驱动能力，电路结构如图 4.10 所示，其内部运放电路结构如图 4.11 所示。在图 4.10 中，VGSP 输出缓冲器具有两种工作模式：当 S1 闭合，S2、S3 打开，电路处于 Buffer 模式。当 S1 打开，S2、S3 闭合，成为具有温度补偿功能的 Buffer 模式。典型的 OLED 显示

面板的发光能力是与温度密切相关的。当温度低于 60 度时，OLED 发光亮度随温度的增加而增强，当温度高于 60 度时，OLED 发光亮度随温度增加而减弱。为了在很宽温度范围内，AMOLED 显示屏发光亮度保持恒定，需要对 AMOLED 显示屏驱动灰阶电压进行温度补偿。此时，输出电压 VGSP\_OUT 随着温度的升高而增加，且结合具有温度补偿功能的 VGMP 输出缓冲器电路来实现伽马曲线的温度补偿功能。

图 4.10 VGSP 输出缓冲器电路结构

Fig 4.10 Structure of VGSP buffer circuit

图 4.11 VGSP 运算放大器电路

Fig 4.11 VGSP operational amplifier circuit

该电路与 VGMP 输出缓冲器电路结构较为类似，同样是由跨导恒定结构，放

大器部分及 class AB 输出级构成。运放结构使用轨到轨输入结构以增大输入电压的共模范围，输入电压的差分对工作在亚阈值区域。为了保证 VGSP 输出缓冲器在整个工作范围内增益保持恒定，该结构增加了跨导恒定功能，通过镜像尾电流源方式来实现。

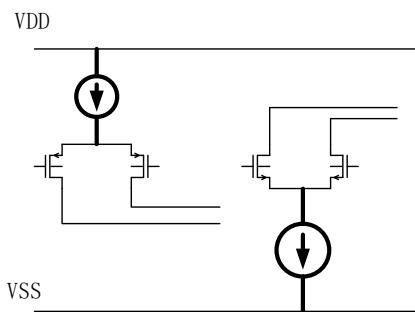

### 4.2.3 跨导恒定电路设计

在放大器中，期望电源电压越低越好，但过低的电源电压会导致运放共模范围降低，而 VGMP 和 VGSP 输出缓冲器电路的电压范围很大，所以该电路采用轨对轨结构。

图 4.12 轨对轨输入级结构

Fig 4.12 rail-to-rail input stage structure

在图 4.12 中电路， $V_{INCMn}$ 的范围在 $V_{GSn} + V_{DSSatn}$ 和 $V_{DD}$ 之间，而 $V_{INCMp}$ 在 $V_{SS}$ 到 $V_{DD} - V_{GSp} - V_{DSSatp}$ 之间，则电路的总共模范围扩大到了 $V_{DD}$ 到 $V_{SS}$ 。

图 4.13 总跨导与共模输入电压的关系

Fig 4.13 relationship between common mode input voltage and total gm

共模输入电压 $V_{INCM}$ 为电源电压一半时两组差分对同时导通，总跨导 $g_m = g_{mn} + g_{mp}$ ，而当 $V_{IN}$ 接近电源电压上下限的时候，只有一个管子工作，此时总的 $g_m$ 也减小了一半。

而总 $g_m$ 的剧烈波动会使得信号发生严重失真，因此当只有一组差分对导通的时候，需要增大 $g_{mn}$ 或 $g_{mp}$ 使得总 $g_m$ 在整个共模输入范围内维持不变，

$g_{mn} + g_{mp} = g_m$ 。当电路的差分对管工作在亚阈值区,  $g_m = I_d/nV_T$  跨导只与电流有关, 因此只需要使得电流增加一倍即可使得跨导也扩大一倍。在本文中使用的偏置电路设计如图 4.14 所示。

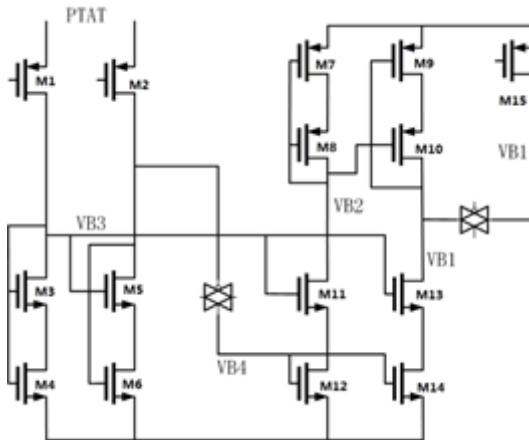

图 4.14 偏置电路

Fig 4.14 bias circuit

在图 4.14 中电路, 电流偏置信号经过 M1, M2 管流入 M3, M4, M5, M6 管组成的电流/电压转换器。在 M1, M2 管导通时, M3, M4 管为 M5 管提供栅压, 而 M5, M6, M11, M12, M13, M14 管为低压共源共栅电流镜, 为运放提供偏置 VB1, VB2, VB3, VB4。

以 VGMP 输出缓冲器电路的主运放结构为例来说明 VGMP/VGSP 输出缓冲器电路中的跨导恒定设计:

图 4.15 VGMP 输出缓冲器电路的主运放结构

Fig 4.15 main amplifier structure of VGMP buffer circuit

图 4.15 中电路主要由三部分: 跨导恒定电路, 放大器电路和输出电路从左到右依次组成。在跨导恒定部分, 输入端电流镜通路传输门由外部输入的数字信号负责开启和关断。当传输门开启后, 可由电流镜通路的管子根据输入电平控制

此功能的开启和关断。

当输入电平  $V_{in}$  为高时 (5.2V 以上), NMOS 对管单独工作, PMOS 对管关断。此时, M5, M6 管导通, 通过 M1, M2, M3 管将 M4 管的栅压拉低, 使 M4 管关断。M16 管导通, 使 M25, M26 管产生的电流通过 M8/9/10/11 管组成的电流镜流入 NMOS 对管。

图 4.16 VGMP 输出缓冲器电路的主运放结构 (高电平)

Fig 4.16 main amplifier structure (high input voltage)

输入电平为低时 (0.6V 以下), NMOS 对管关断, PMOS 对管单独工作。此时 M23/24 管导通, 通过 M17/18/19 管抬高 M16 管的栅压, 使其关断, M4 管导通, 使 M31/32 产生的电流, 由 M12/13/14/15 管组成的电流镜通路流入 PMOS 对管。

图 4.17 VGMP 输出缓冲器电路的主运放结构 (低电平)

Fig 4.17 main amplifier structure (low input voltage)

输入电平为中间值时 (0.6V-5.1V), NMOS 对管和 PMOS 对管同时工作。此时 M4/16 管都关断, 关闭了两个电流镜通路, 不进行电流的补偿。

图 4.18 VGMP 输出缓冲器电路的主运放结构（中间电平）

Fig 4.18 main amplifier structure (intermediate input voltage)

由于差分对管均工作在亚阈值区，因此跨导恒定部分电路以一倍电流镜补偿电流即可实现跨导恒定功能。放大器输入对管部分使用轨到轨结构输入，M42 管为输出端调整管。

#### 4.2.4 VGMP 输出缓冲器的仿真和分析

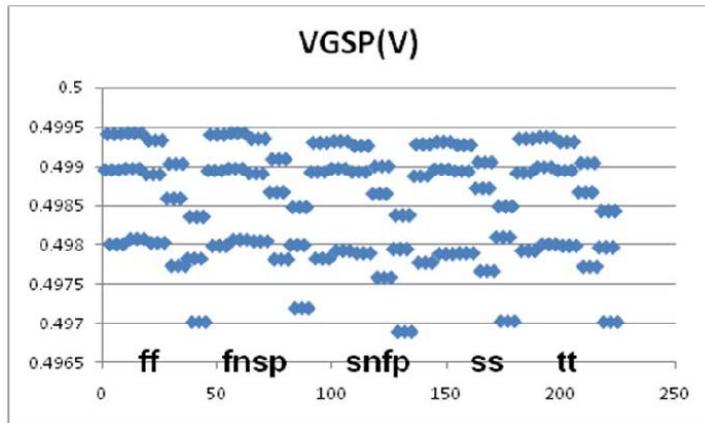

##### (1) 直流仿真

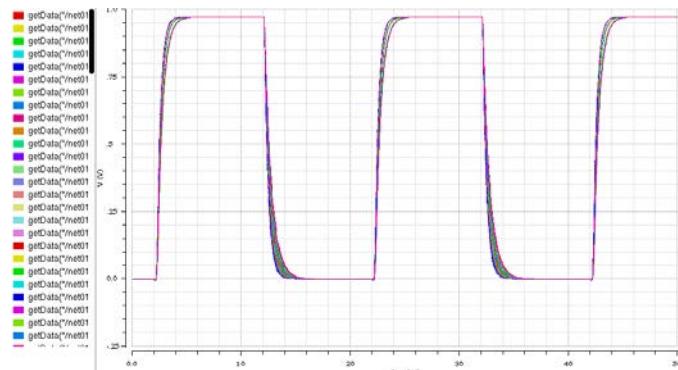

电路处于 Buffer 模式，输出电压  $VGMP=4.2V$ ，负载电流  $400 \mu A$  时 PVT 仿真结果如图 4.19 所示。

图 4.19 VGMP 输出缓冲器的输出电压

Fig 4.19 VGMP output voltage

可以看出，PVT 变化对输出电压  $VGMP$  影响不大。

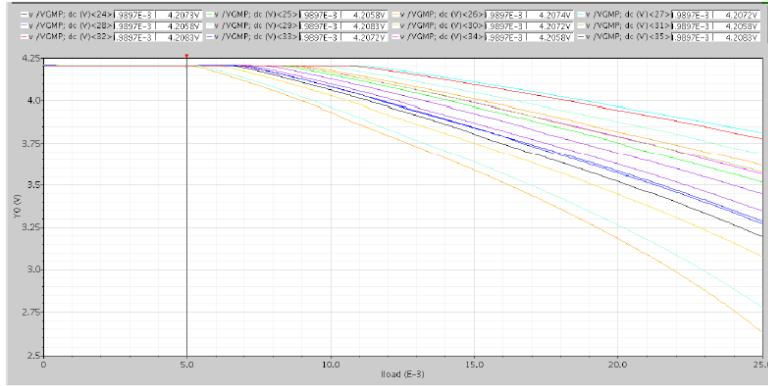

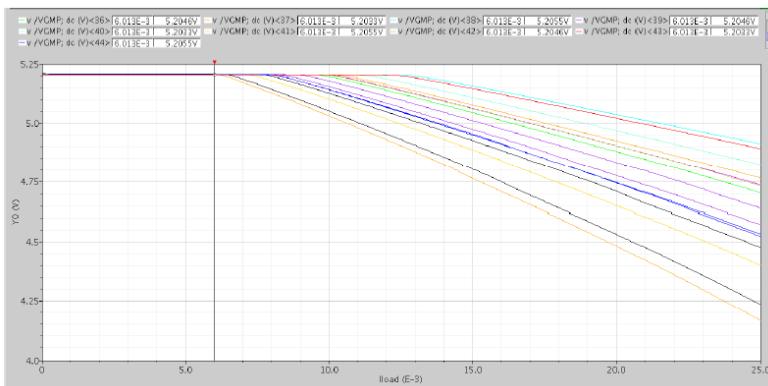

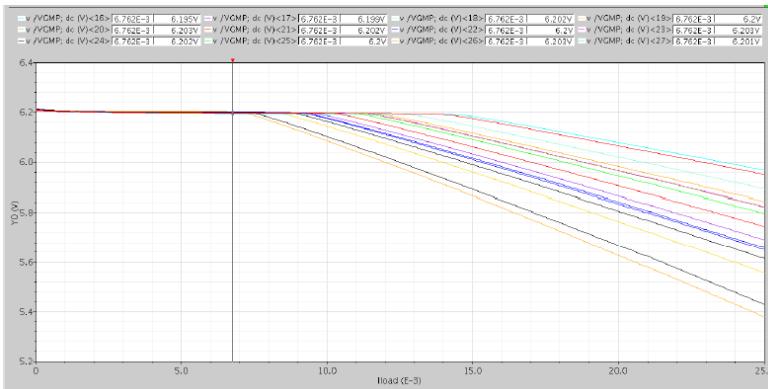

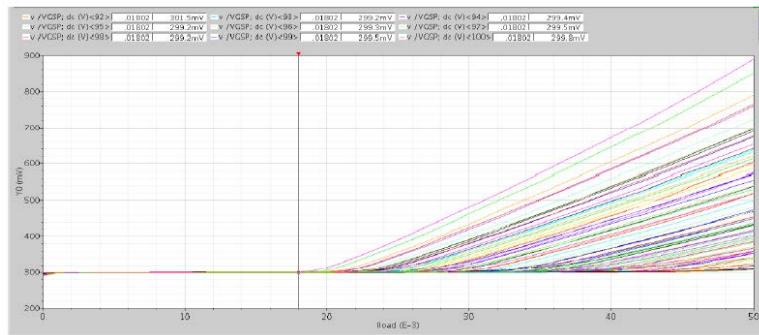

##### (2) 最大负载电流

电路处于 Buffer 模式，电源电压分别为  $4.5V/5.5V/6.5V$ ，且输出电压  $VGMP$  相应为  $4.2V/5.2V/6.2V$  时，电路的最大负载电流仿真结果如图 4.20 所示。

(a) 电源电压 4.5V, VGMP=4.2V

(b) 电源电压 5.5V, VGMP=5.2V

(c) 电源电压 6.5V, VGMP=6.2V

图 4.20 不同电源电压和 VGMP 电压下的负载电流

Fig 4.20 Load current at different VGMP and power voltage

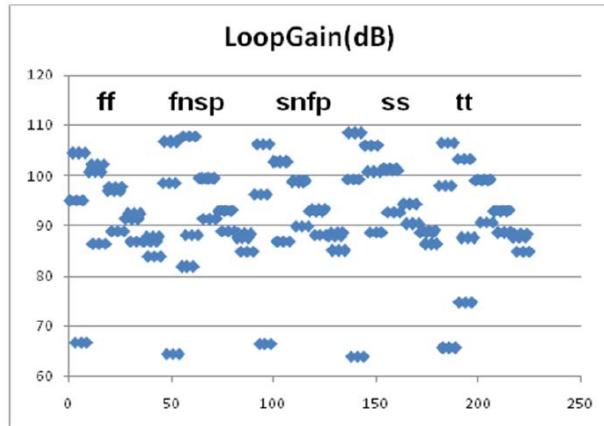

可以发现当负载在一定范围内变化的时候，输出的负载电流是可以保持稳定的。

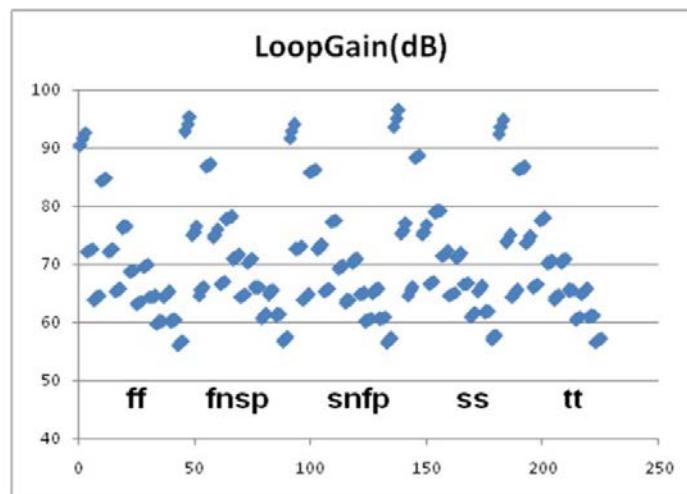

### (3) 稳定性分析

电路处于 Buffer 模式，输出电压 VGMP=4.2V，负载电流  $400 \mu A$  时，电路的稳定性仿真结果如图 4.21 所示。

(a) 环路增益

(b) 相位裕度

(c) GBW

图 4.21 VGMP 输出缓冲器电路稳定性分析

Fig 4.21 stability analysis of VGMP buffer circuit

从仿真结果可以看出，环路增益都在 60dB 以上，相位裕度可以达到 80°，满足设计要求。

#### (4) PSRR 分析

电路处于 Buffer 模式, 输出电压  $VGMP=4.2V$ , 负载电流  $400 \mu A$  时, 电路的 PSR 仿真结果如图 4.23 所示。

图 4.22 VGMP 输出缓冲器电路的电源抑制比

Fig 4.22 PSRR of VGMP buffer circuit

从仿真结果可以看出, 电源抑制比在低频  $25kHz$  处大于  $40dB$ ,  $100kHz$  处大于  $30dB$ , 满足设计要求。

### (5) 瞬态仿真

电路处于 Buffer 模式, 输出电压  $VGMP=4.2V$ , 负载电流  $400 \mu A$  时, 电源电压从  $4.5V$  到  $6.5V$  之间进行变化, 电路的瞬态响应过程如图 4.23 所示。

图 4.23 VGMP 输出缓冲器电路电源电压变化瞬态响应

Fig 4.23 power supply fluctuation transient response of VGMP buffer circuit

电路处于 Buffer 模式, 输出电压  $VGMP=4.2V$ , 负载电流在  $0$  和  $400 \mu A$  之间

进行变化时，电路的瞬态响应过程如图 4.24 所示。

图 4.24 VGMP 输出缓冲器电路的负载变化瞬态响应

Fig 4.24 load current fluctuation transient response of VGMP buffer circuit

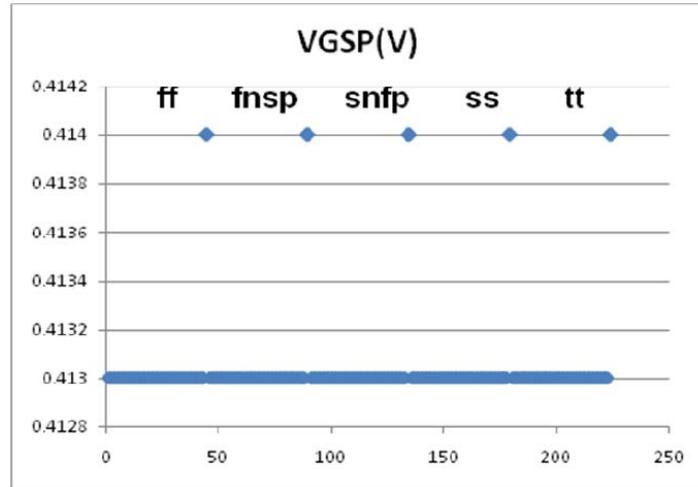

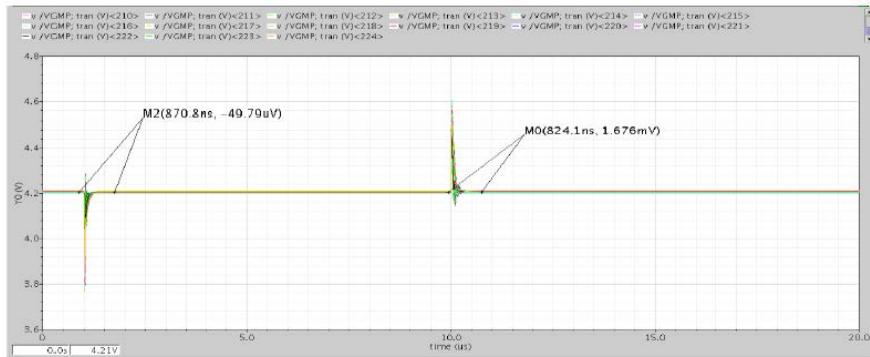

#### 4.2.5 VGSP 输出缓冲器的仿真和分析

##### (1) 直流仿真

电路处于 Buffer 模式，输出电压 VGSP=0.5V，负载电流  $400 \mu A$  时 PVT 仿真结果分别如图 4.25 所示。

图 4.25 VGSP 输出缓冲器电路的输出电压

Fig 4.25 output voltage of VGSP buffer circuit

可以看出，PVT 变化对输出电压 VGSP 影响不大。

##### (2) 最大负载电流

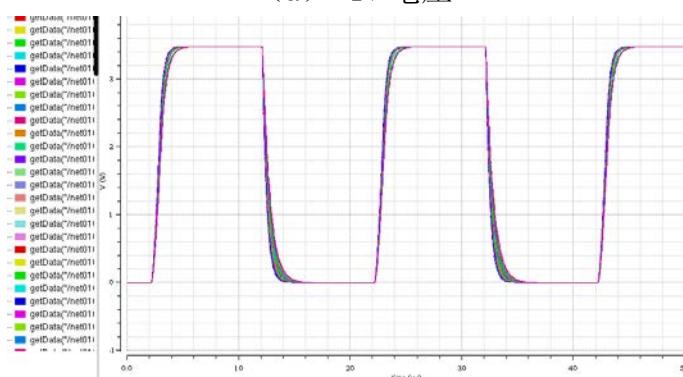

电路处于 Buffer 模式，输出电压 VGSP 为  $0.3V/0.5V$  时，电路的最大负载电流仿真结果如图 4.26 所示。

(a) VGSP=0.3V

(b) VGSP=0.5V

图 4.26 VGSP 输出缓冲器电路的最大负载电流仿真

Fig 4.26 Maximum current load simulation of VGSP buffer circuit

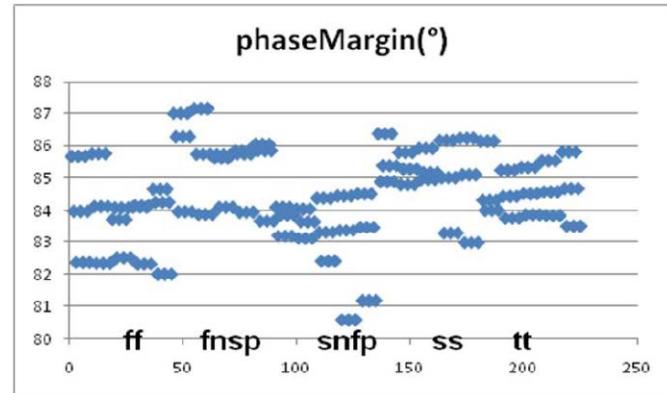

### (3) 稳定性分析

电路处于 Buffer 模式, 输出电压 VGMP=4.2V, 负载电流  $400 \mu A$  时, 电路的稳定性仿真结果如图 4.27 所示。

(a) 环路增益

(b) 相位裕度

(c) GBW

图 4.27 VGSP 输出缓冲器电路的稳定性仿真

Fig 4.27 stability simulation of VGSP buffer circuit

从仿真结果可以看出，环路增益都在 55dB 以上，相位裕度可以达到 80°，满足设计要求。

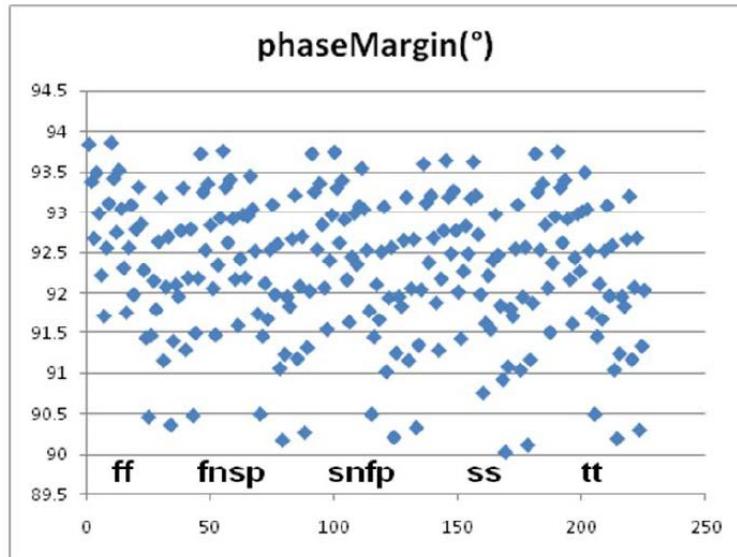

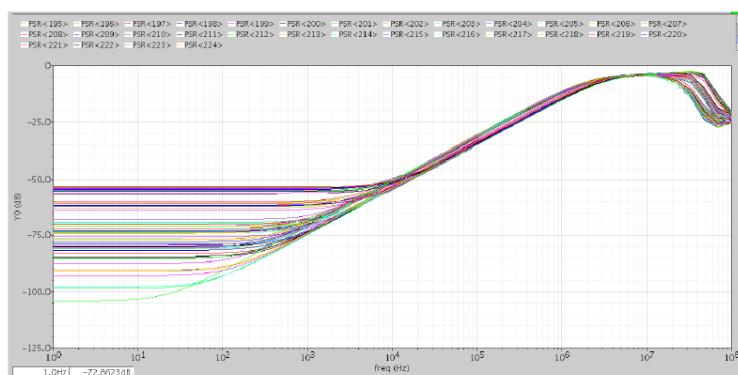

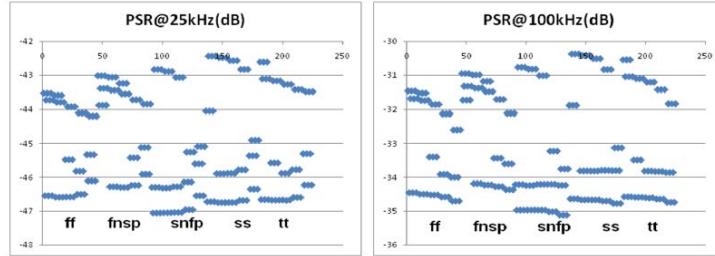

#### (4) PSRR 分析

电路处于 Buffer 模式，输出电压  $VGSP=0.5V$ ，负载电流  $400 \mu A$  时，电路的 PSR 仿真结果如图 4.31 所示。

图 4.28 VGSP 输出缓冲器电路的电源抑制比

Fig 4.28 PSRR of VGSP buffer circuit

从仿真结果可以看出，电源抑制比在低频 25kHz 处大于 40dB，100kHz 处大于 30dB，满足设计要求。

### (5) 瞬态仿真

电路处于 Buffer 模式，输出电压  $VGSP=0.3V$ ，负载电流  $400\mu A$  时，电源电压从  $4.5V$  到  $6.5V$  之间进行变化，电路的瞬态响应过程如图 4.29 所示。

图 4.29 VGSP 输出缓冲器电路电源电压变化瞬态响应

Fig 4.29 power supply fluctuation transient response of VGSP buffer circuit

电路处于 Buffer 模式，输出电压  $VGSP=0.3V$ ，负载电流在  $0$  和  $400\mu A$  之间进行变化时，电路的瞬态响应过程如图 4.30 所示。

图 4.30 VGSP 输出缓冲器电路负载变化瞬态响应

Fig 4.30 current load fluctuation transient response of VGSP buffer circuit

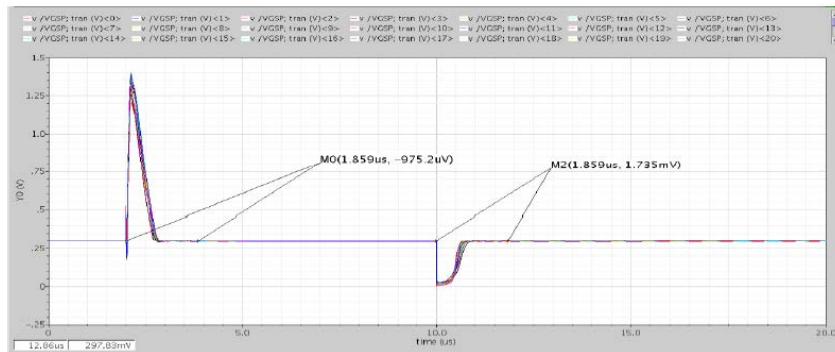

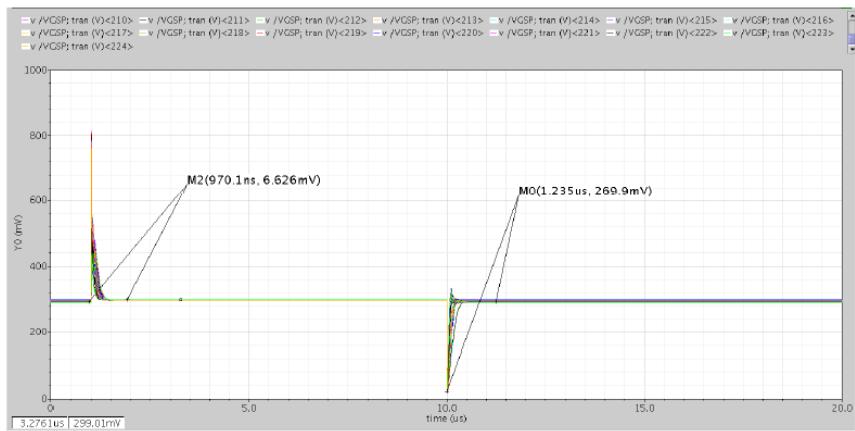

#### (6) VGMP, VGSP 同时启动仿真结果

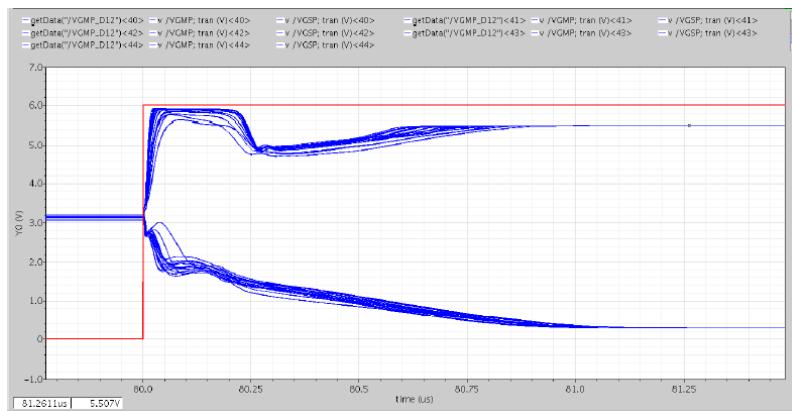

电源电压为 6V, VGMP、LVGSP 输出缓冲器电路都处于 Buffer 模式, VGMP 输出为 5.5V, VGSP 输出电压 VGSP=0.3V 时, 且 VGMP 和 VGSP 输出缓冲器电路的使能信号在 AVDD 稳定之后同时有效, 电路的启动过程如图 4.31 所示。

图 4.31 VGMP 和 VGSP 输出缓冲器电路同时启动瞬态响应

Fig 4.31 transient response of VGMP and VGSP buffer circuit

### 4.3 拐点和输出缓冲器电路

在本文的设计中, 电路是依靠电阻串分压的方式来调节输出的灰阶电压大小的, 电阻大小往往能达到数十千欧。主要起控制功能的数字逻辑模块的负载驱动能力很差, 为了保证灰阶电压的输出精度以及建立速度, 需要在电阻负载和控制模块之间加上缓冲器电路以提高电路性能。拐点缓冲器电路的作用是为了在三段式设计的伽马校正曲线中充当中间两个拐点处灰阶电压的产生和传输。

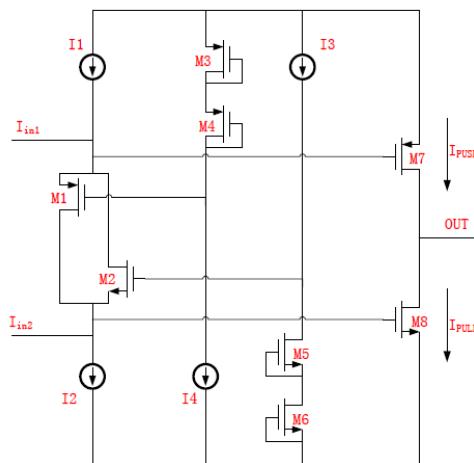

### 4.3.1 电路设计

拐点与输出缓冲器是进行斜率调节时，作为斜率调节点的电压缓冲器。在设计时应当考虑以下因素。首先，必须满足输入电压摆幅的要求。电压摆幅是由灰阶电压曲线决定的，因此轨到轨的输入级为常用手段。其次，需要有短时间内放出高输出电流的能力。在伽马校正电路中电压缓冲器往往需要驱动大小为数千欧的负载或者为大电容充电。由于行列信号施加的时间很短，因此这个过程必须在极短的时间内完成。则缓冲器电路的大电流输出能力成为重要指标。最后，缓冲器电路的功耗必须尽可能的小。

本设计中的伽马校正电路需要为 DAC 部分输送 65 个不同的灰阶电压，相应的需要使用 65 个缓冲器。如此庞大的用量对缓冲器自身的功耗提出了很高的要求，因此在设计中需要注意降低静态电流，以压低电路功耗。

鉴于 DAC 电路对于大负载的驱动能力不高，负载会破坏系统的增益和稳态，影响输出电压。因此需要增加一个缓冲器电路来驱动后级的大负载。输出缓冲器作为控制电路和像素电路的连接装置，其驱动负载能力的强弱决定了输出图像显示效果的好坏。

图 4.32 拐点与输出缓冲器电路

Fig 4.32 breaking point buffer circuit

所设计的输出缓冲器整体结构示意图如图 4.33 所示, 由输入级、输出级和增益级构成。考虑显示面板所需要的输出电压范围为  $0.3V \sim 6.3V$ , 电压范围接近电源到地, 要求缓冲器能够支持全摆幅范围的输入输出。所以运放部分选择使用轨到轨结构的输入级以及 class AB 输出级<sup>[42]</sup>。考虑到电路对功耗的要求, 本文利用运放差分对管工作在亚阈值区, 跨导和电流成线性关系, 采取降低静态电流的方法达成降低功耗的目的。考虑到电路对输出精度的要求, 输出电压偏差为  $\pm 3mv$ , 输出缓冲器为单位增益负反馈结构<sup>[43-44]</sup>。因此需要让该缓冲器具备较大的开环增益。增益级使用 Cascode 结构可以利用输出阻抗的增加, 来提升开环增益, 并通过频率补偿电路提高稳定性。此外, 考虑实际显示面板上有众多通道, 需要减少每一个缓冲器的静态电流, 因此采用了 class AB 输出级。

### 4.3.2 Class AB 输出级设计

Class AB 类输出级在驱动较小的电阻和较大的电容时，相比于传统输出级具有很多优势。能够在流过较小静态电流的情况下，传输很大的电流到负载上且不受电源电压的影响，不会影响信号通路直流增益。在电流发生波动的时候不会导致稳定性的下降，可以在低电压下工作。结构简单，不会显著增加面积。综合以上条件，本方案使用 class AB 结构作为运放的输出级设计。

图 4.33 Class AB 输出级

Fig 4.33 class AB output stage

如图 4.33 所示, 该结构的工作流程为: 由前级进入的输入信号  $V_{in1}$  降低的同时, 造成 M1 管的偏置电流上升。而在同一条支路上的 M1, M2 管的总电流保持不变, 则 M2 管的偏置电流势必下降。在镜像电流源的作用下, 施加于 M2 栅极的电

压是能够确定不变的，所以 M2 管源端的电压会被抬升。这造成 M8 管栅极电压的上升。对各管的参数进行调节，可确保 M7，M8 两个功率管的栅压同步变化。在整个系统中，M1，M2 管作为悬浮电压源起平衡作用。而 M3，M4 管为 M1 管提供栅极偏置电压。M5，M6 管则负责为 M2 管提供栅极偏置电压。

此时 M7 与 M8 管已经可以保证输出电压的充分稳定了。两个功率管均处于饱和区。此外，class AB 输出级还能达到很可观的动态静态电流比，提升系统的整体效率。当 M7，M8 管的栅极电压分别被固定在  $V_{DD} - V_{TH}$  与  $V_{SS} + V_{TH}$  的时候，输出电压的幅度可以达到  $V_{SS} + V_{Dsat}$  到  $V_{DD} - V_{Dsat}$ 。这样就足以把静态电流维持在低水平状态，降低了缓冲器电路的总功耗，而同时带来的问题就是输出电压需要花费较长的时间来完成建立。所以需要结合电路的具体设计指标，在系统功耗和响应时间上做出妥协来完成最终的设计工作。

### 4.3.3 Cascode Miller 补偿

在运放的各项设计指标中，系统稳定性无疑是其中最重要的设计指标之一。对于二级及以上的放大器系统来说频率补偿已经成了一种必不可少的手段了。密勒补偿作为最经典最常用的频率补偿方式，利用在输入输出间的反馈回路上加入电容，使得两级运放之间产生的极点往原点偏移。而第二级放大器部分产生的极点往主极点相反的方向偏移，实现提高相位裕度和负反馈系统稳定性的目的。通过计算可得，当负载电容为  $C_L$  的时候，为了补偿系统使得相位裕度能够达到 60 度以上，则需要在反馈回路接上大小为  $0.22C_L$  的密勒电容。结合本文可以发现，像素电路负载中的电容大小普遍达到了 pF 级别。如果只使用常规的密勒补偿方式，那么参与频率补偿的电容体积同样会很大造成芯片空间的大量浪费。同时大电容的充放电过程非常缓慢，如果采用了高静态电流的设计来弥补反应速度的不足，则违背了缓冲器电路低功耗的设计初衷。综上可知，常规的密勒补偿方式对于需要快速建立灰阶电压的缓冲器电路来说是很不合适的。

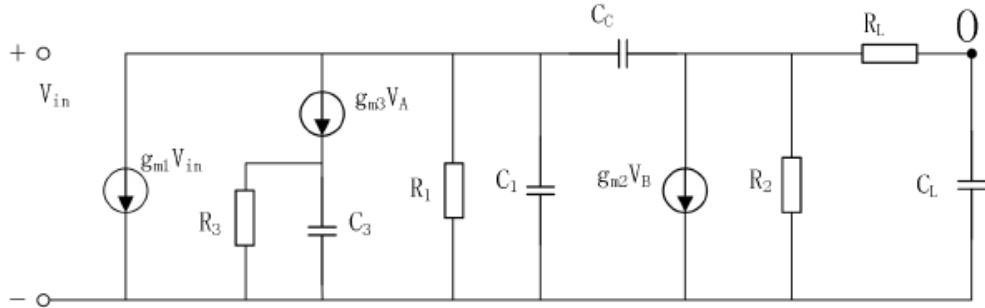

通过对密勒补偿适电路的改进，Cascode Miller 补偿方式于 20 世纪 80 年代诞生。该补偿方式是通过把补偿电容一端移动到前一级的共源共栅器件一边，将经典密勒补偿方式中的第一级输出到系统输出的前馈通路利用 cascode 方式截断，所以该方法被称为 cascode Miller 补偿<sup>[45]</sup>。这种方法依然能够完成经典密勒补偿的任务即将两个极点拉开距离保证相位裕度，但密勒补偿的电容可以按比例同时补偿第一级和第二级的输出。从图 4.34 中 cascode Miller 补偿的小信号等效模型的量化分析可以发现，使用了 cascode Miller 补偿的电路利用很小的电容即完成了把主次极点拉开的工作<sup>[46]</sup>。

如图 4.32 所示的缓冲器为本文伽马校正电路所使用的输出缓冲器，使用较小的电容 C 即可完成频率补偿的任务。通过下面的小信号等效模型，可以得到补偿电容 C 的具体参数。

图 4.34 缓冲器等效小信号模型

Fig 4.34 Small-signal equivalent model of buffer

图 4.34 中  $g_{m1}$  为第一级运放的等效跨导， $R_1$  和  $C_1$  为运放的负载电阻和电容。第二级放大电路的等效跨导为  $g_{m2}$ ， $R_2$ 、 $R_L$ 、 $C_L$  为系统的输出负载。补偿回路的跨导为  $g_{m3}$ ，负载为  $R_3$ 、 $R_L$ 、 $C_L$ 。在该等效电阻  $R_L$  可作为补偿电阻来补偿出现的零点，0 点为电路的输出端。综合以上参数，可以得到电路的传输函数：

$$\frac{V_O}{V_{in}} = \frac{g_{m1}(g_{m2}g_{m3} - s^2 C_c C_3)(1 + s R_L C_L)}{a s^3 + b s^2 + c s + d} \quad (4.6)$$

其中

$$a = C_3 C_T^2 + g_{m3} C_c C_L C_3 R_L \quad (4.7)$$

$$b = g_{m3} C_L (C_3 + g_{m2} R_L C_c) + g_{m3} C_c C_3 \quad (4.8)$$

$$c = g_{m2} g_{m3} C_c \quad (4.9)$$

$$d = \frac{1 + g_{m3} R_1}{R_1 R_2 R_3} \quad (4.10)$$

$$C_T^2 = C_1 C_L + C_1 C_c + C_L C_c \quad (4.11)$$

由传输函数可以得到系统的三个零点： $Z_{1,2} = \pm \sqrt{\frac{g_{m2} g_{m3}}{C_c C_3}}$ ， $Z_3 = -\frac{1}{R_L C_L}$

其中  $Z_1$  和  $Z_2$  距离 GBW 点较远，对幅频特性曲线的影响有限。而  $Z_3$  作为起补偿作用的零点可以极大的影响系统的相位裕度。由于极点  $p_1$ 、 $p_2$  和  $p_3$  的各自相距离很远，则可据此得到系统的阻尼因子：

$$\xi = \sqrt{\frac{g_{m3} C_L}{4 g_{m2} C_c C_3 (C_1 + C_c + g_{m3} R_L C_c)}} (C_3 + g_{m2} R_L C_c) \quad (4.12)$$

从式 4.12 可以看出相位裕度与  $g_{m3}$  和  $R_L$  有关。如果提升  $R_L$  的值的可以大大减少补偿电容  $C_c$  的大小，起到压缩芯片面积的作用。

#### 4.3.4 仿真分析

在仿真环境为电源电压 AVDD=6.5V，温度为 27°C，典型工艺角；取 VGMP=6.2V，

VGSP=1.8V。取偏置电路输入电流 gamma\_bias\_iref=15uA, 寄存器控制字为 0110 1000011, 可得到仿真结果。

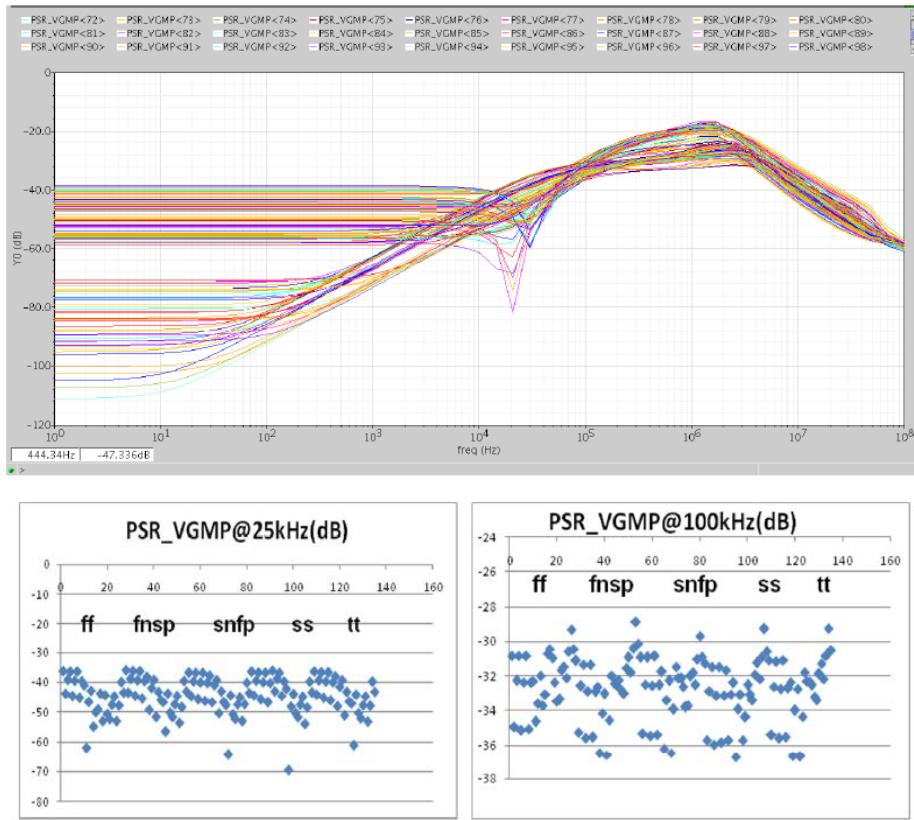

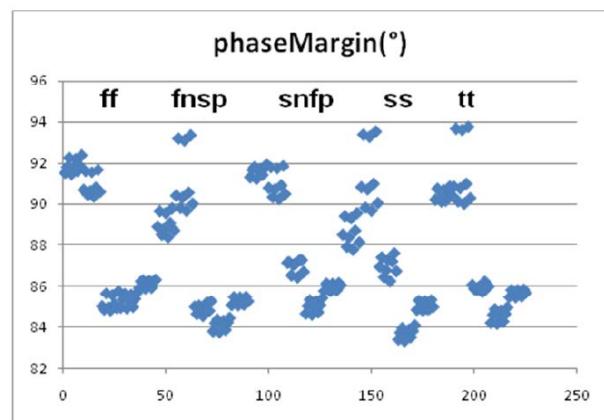

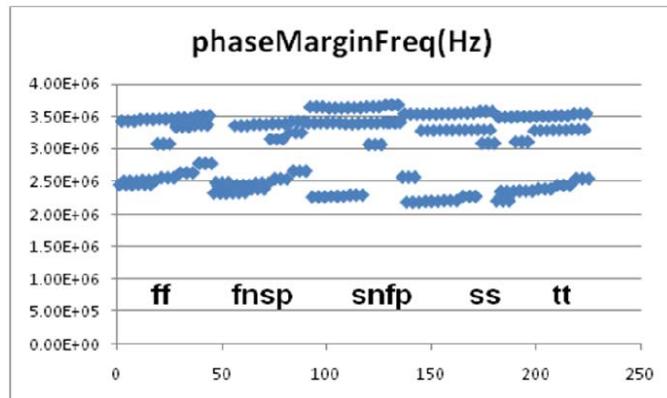

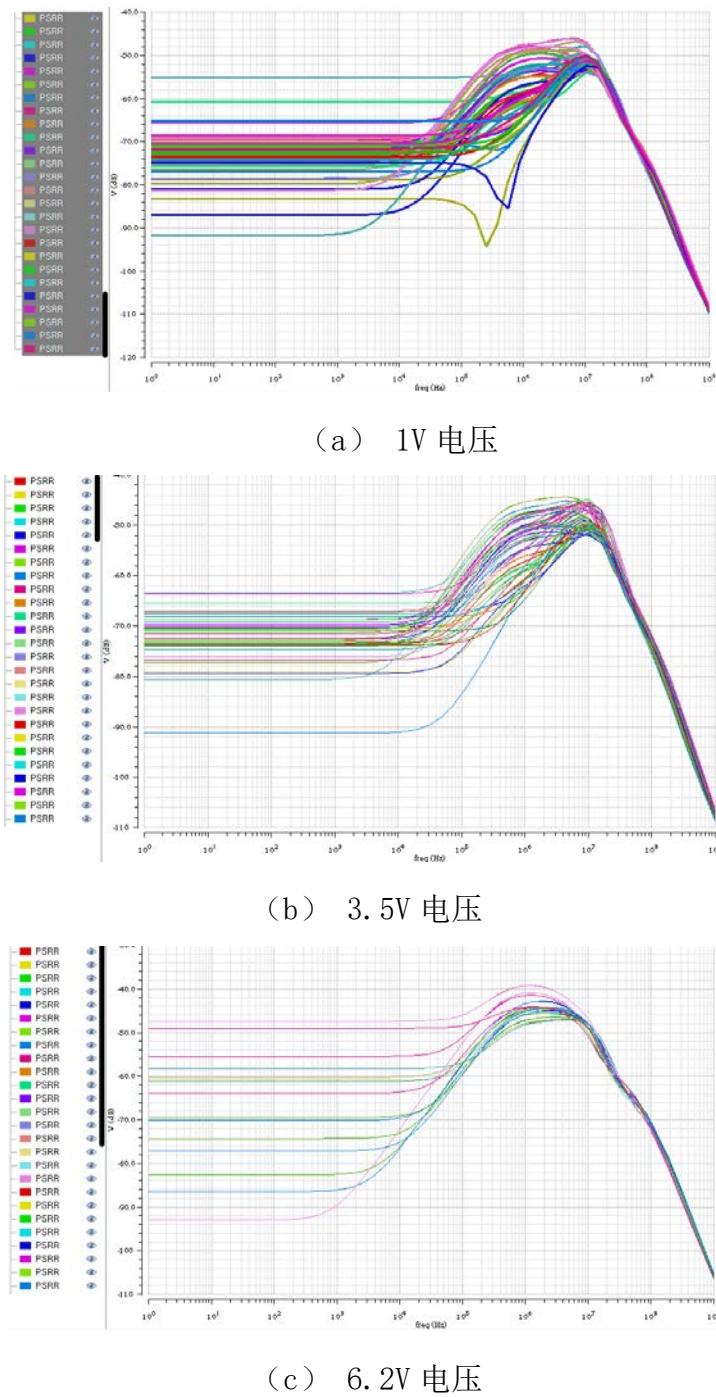

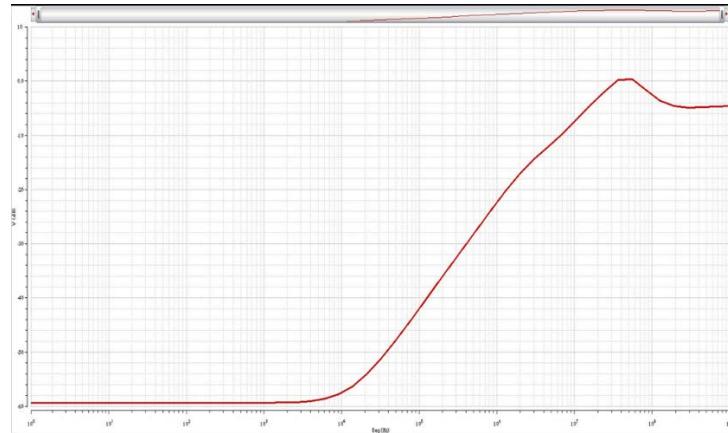

### (1) PSRR 分析

仿真结果取了输入电压在 1V-6.2V 时的仿真结果。如图 4.35 所示, 在低频时, 电源抑制比为 70dB, 1.6MHz 时, 电源抑制比依然有 50dB。

图 4.35 不同输入电压下的电源抑制比

Fig 4.35 PSRR at different input voltage

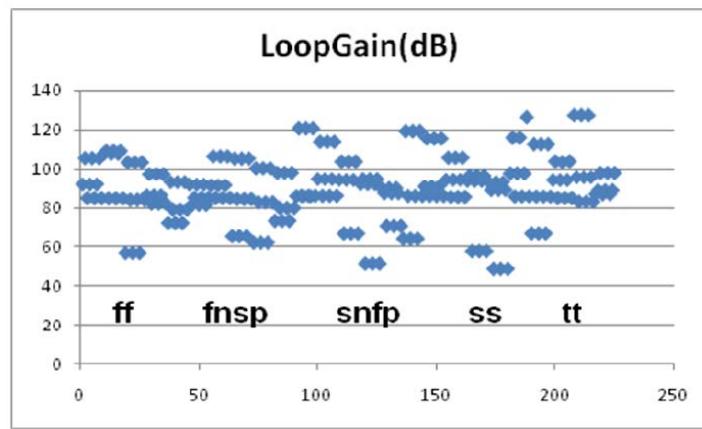

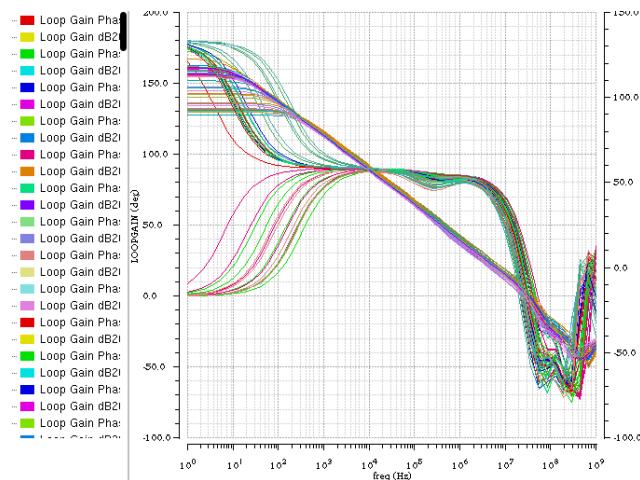

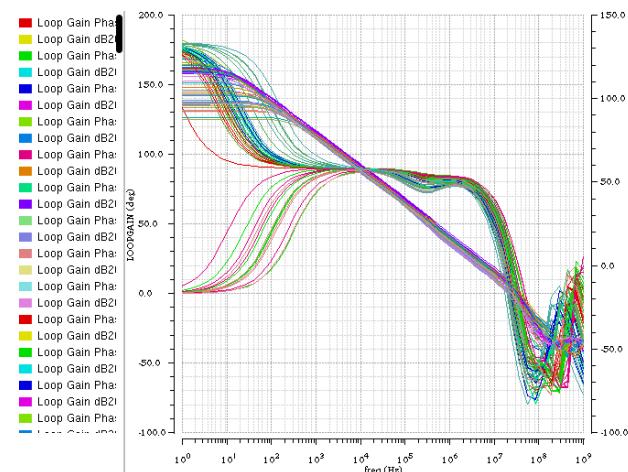

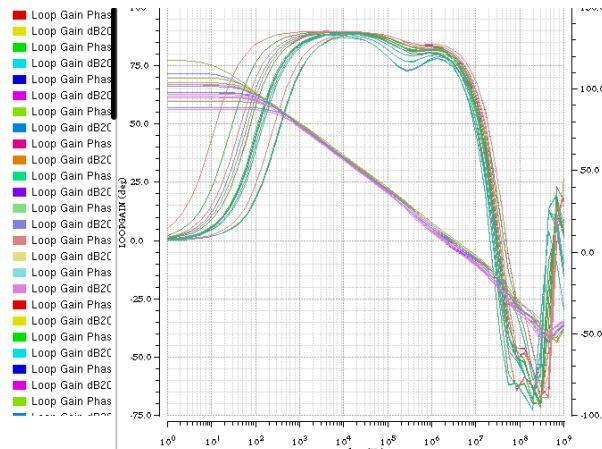

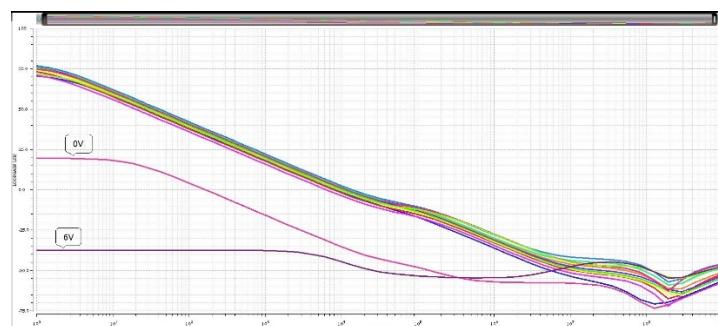

## (2) STB 分析

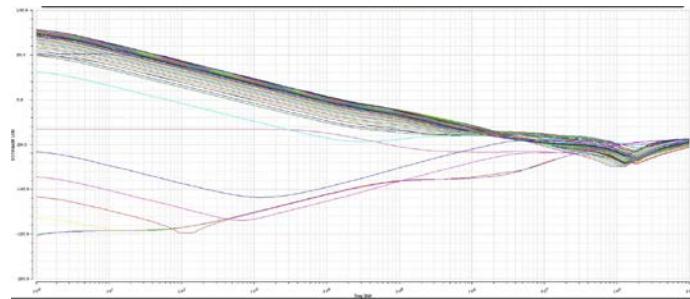

电源电压为 6.5V 条件下, 对输出缓冲器取不同输入的电压范围下分别扫描, 其幅频特性曲线如图 4.36 所示。可以看出, 在整个输入电压范围内, 输出缓冲器的直流增益都满足在 70dB 以上, 相位裕度在 60deg 以上, 可以保证输出缓冲器闭环环路的稳定性。在典型工作的 3.3V 左右时, 增益可达 129dB, 相位裕度 75deg, 增益带宽 9.4MHz, 增益满足设计要求、稳定性高。

(a) 1V 电压

(b) 3.5V 电压

(c) 6.2V 电压

图 4.36 不同输入电压下的稳定性仿真

Fig 4.36 stability simulation of different input voltage

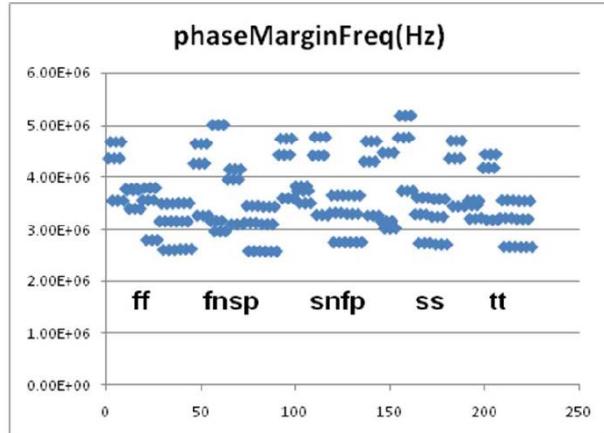

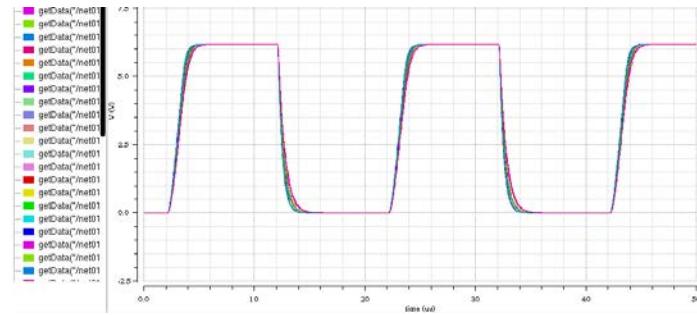

### (3) 建立时间

对输出缓冲器的建立时间进行了仿真，达到精度 90% 时，从 0.2V 到 6.2V 的建立时间为 1.49us。达到精度 99% 时，建立时间为 2.49us。达到精度 99.9% 时，建立时间为 3.5us。

(a) 1V 电压

(b) 3.5V 电压

(c) 6.2V 电压

图 4.37 不同输入电压下的建立时间仿真

Fig 4.37 set up time simulation at different input voltage

#### 4.4 伽马校正电路的级联仿真

在电源电压分别为 3.7V 和 6.5V, 温度为 27 °C, 工艺角为  $tt$ , 电阻为 typ 的仿真条件下, 对伽马校正电路进行整体仿真。

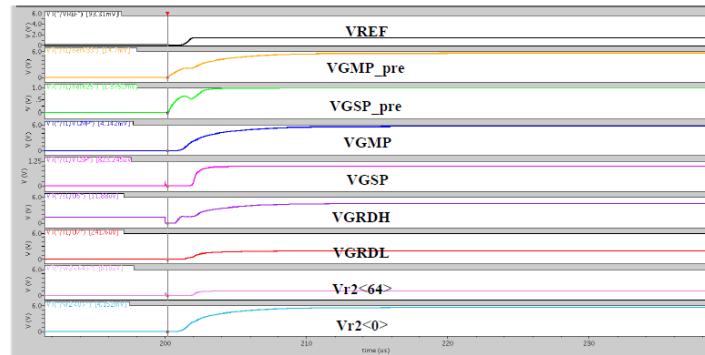

##### (1) 启动时序

当带隙基准、AVDD 电荷泵、数字电路等模块正常工作以后, 依次启动伽马校正电路内部各模块, 其过程如图 4.40 所示。

图 4.38 伽马校正电路的启动时序

Fig 4.38 Start sequence of GAMMA correction circuit

从仿真结果可以看出, 整个伽马校正电路电压稳定时间约  $20 \mu s$ , 满足电路的设计要求。

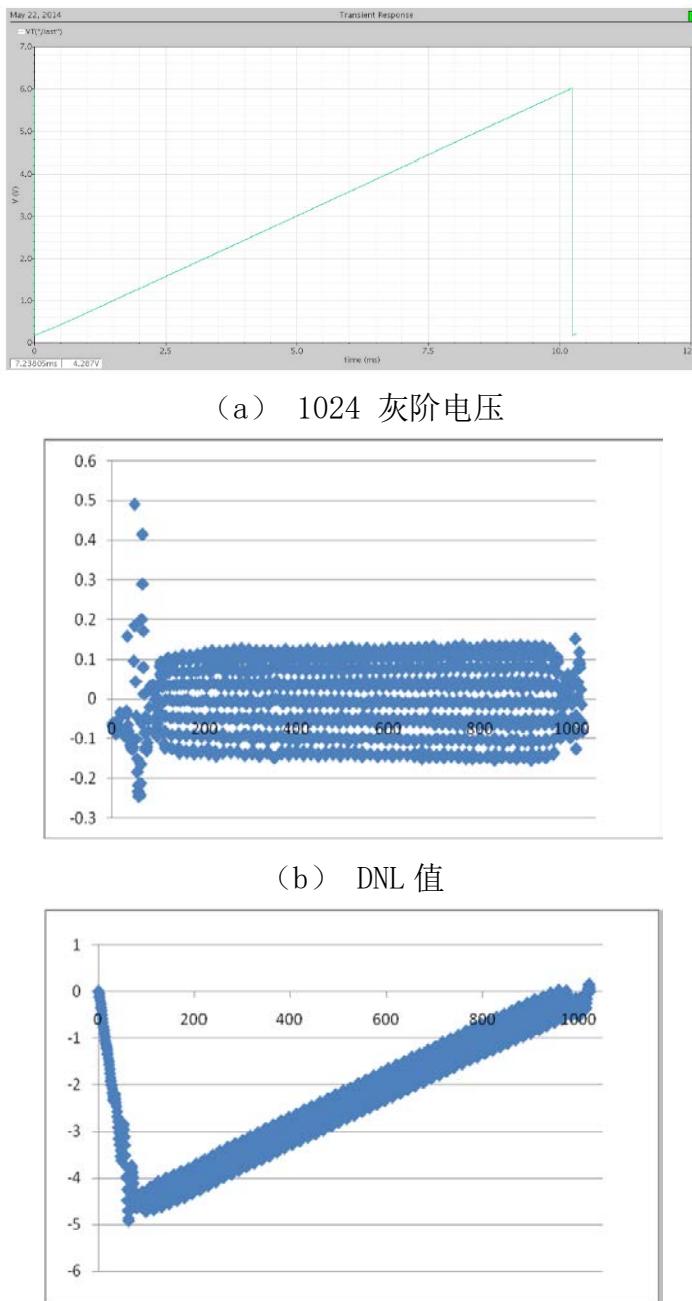

##### (2) DNL 和 INL

伽马校正和位于列驱动中的线性 DAC 进行级联仿真, 可以看作为一个两级线性 DAC 级联。当配置伽马曲线为一条直线,  $VGMP=6V$ 、 $VGSP=0.3V$  时, 可以得到 1024 灰阶电压, 从而可以计算出该线性 DAC 的 DNL、INL 值, 仿真结果分别如图 4.39 所示。

图 4.39 DNL 和 INL 值仿真

Fig 4.39 DNL and INL simulation

仿真结果表明本文的伽马校正电路实现的误差小于 3mV，并且符合本文的三段式伽马校正曲线在中压范围精度最高、低压其次、高压精度最低的要求，在 0.2V~6.3V 的宽输入范围内均具有良好的精度和线性度。

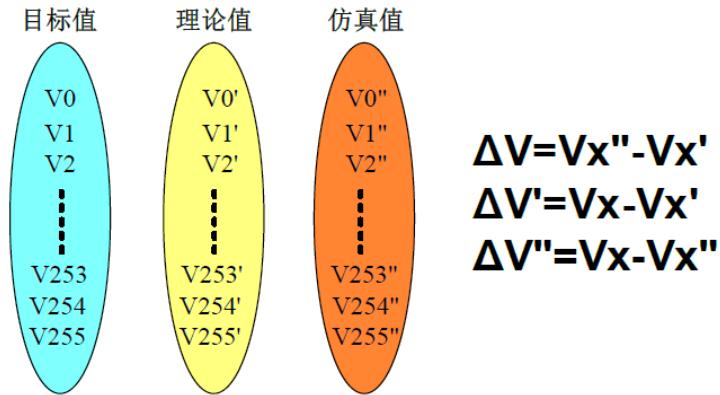

### (3) 误差比较

对于伽马校正电路来说，目标是实现屏厂商需要的灰阶电压（记为目标值）。但是由于硬件结构的限制，实际芯片能实现的伽马曲线（记为仿真值）与目标值之间有差距。而在屏厂商拿到芯片时，其不需要了解电路结构，只需要根据芯片

设计厂家提供的使用说明调节出所需要的伽马曲线（记为理论值）。但是芯片厂商提供的理论计算方法得出的值，与实际电路得出的可能存在误差。图 4.40 给出了目标值、理论值和仿真值之间的误差关系表示。

图 4.40 伽马校正系统误差

Fig 4.40 GAMMA correction system error

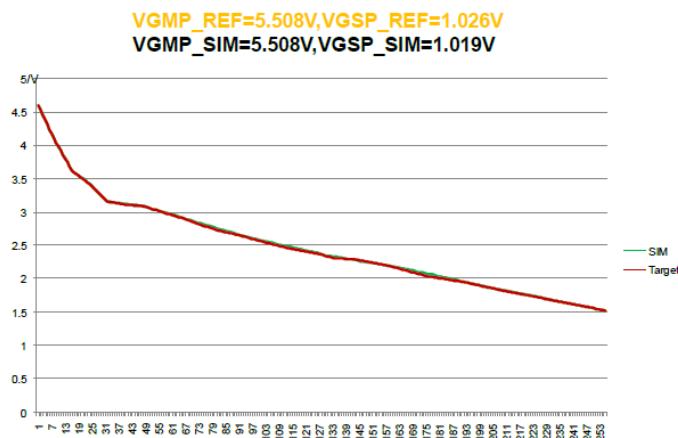

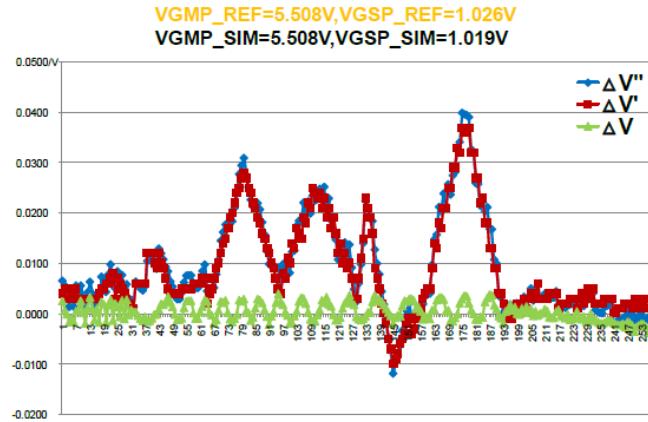

下面将用一条屏厂商提供的伽马曲线的仿真结果，且比较伽马校正电路存在的误差。图 4.41 为 VGMP 电压为 5.508V，VGSP 电压为 1.019V 时产生的实际仿真曲线与理想曲线的对比。

图 4.41 伽马曲线仿真结果

Fig 4.41 GAMMA curve simulation result

图 4.42 伽马曲线误差比较

Fig 4.42 error comparison of GAMMA curve

由图 4.42 可知, 幅度电压仿真值 VGMP\_SIM=5.508V、VGSP\_SIM=1.019V; 理论计算值 VGMP\_REF=5.508V、VGSP\_REF=1.026V, 从比较结果可以看出, 理论值和仿真值基本相等, 但是理论值和目标值、仿真值和目标值在某些点存在较大误差。这主要是由于采用屏厂商给的伽马曲线的关键灰阶电压和芯片实现的不一样造成的。如果要消除仿真值和目标值之间的误差, 可以根据屏厂商需要的伽马曲线进行定制。

## 4.5 伽马校正电路的版图及后仿

### 4.5.1 伽马校正电路的版图设计

在完成电路结构的设计, 确定了器件的尺寸和工作状态以后, 接下来进行版图设计, 完成版图设计后即可交付流片。版图设计的目的是将设计好的电路按一定的规则流程变成产品, 这个过程并不仅仅是将功能模块进行组合拼接, 也需要设计人员精心设计, 使得各功能模块的相互结合不影响电路的性能。

随着器件尺寸的逐渐缩小, 电路性能方面的要求也越来越高。小尺寸器件提高了电路的响应速度, 但对相邻器件之间的相互干扰更加敏感, 这些因素必须考虑。本文设计的 LDO 与缓冲器对精度和响应速度均十分敏感, 其性能直接影响整个系统的性能指标。

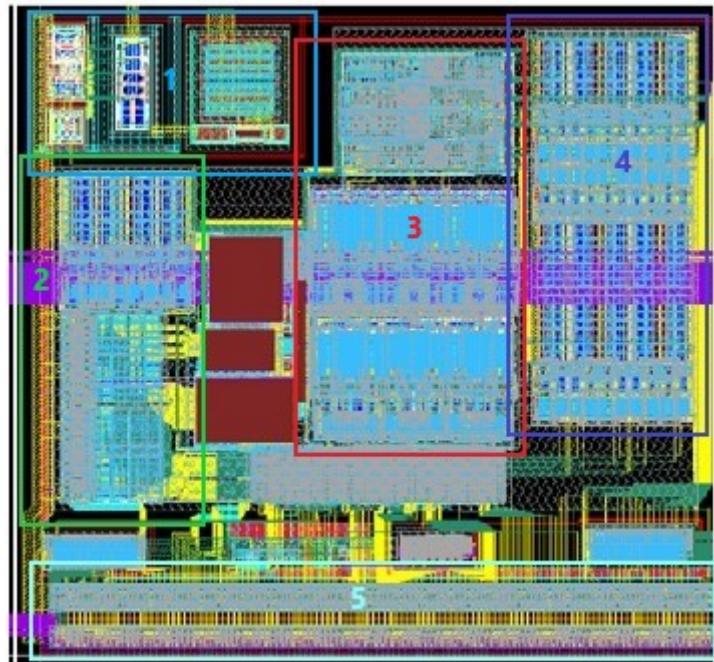

图 4.43 伽马校正电路的版图

Fig 4.43 Lay out of gamma correction circuit

图 4.43 为伽马校正电路的版图, 工艺为 UMC 80nm, 共一层多晶硅、四层金属。其中, 序号为 1 的是使能信号产生模块控制电路的版图, 它产生使能控制信号。序号为 2 的是 VGMP/VGSP 电压产生电路的版图, 通过中央的电阻串分压将产生的 VGMP 和 VGSP 电压, 输出给版图中央的 VGMP/VGSP 输出缓冲器电路 (序号 3), 该部分电路经过位于版图下方线性 DAC 相连接的控制电路 (序号 5) 控制电阻串的大小, 以输出不同的灰阶电压。拐点与输出缓冲器电路的版图为序号 4 的部分。各个功能模块通过传输线, 信号线, 负载线与电源线将整个伽马校正电路的各个组成部分连接起来。

本文设计的 LDO 以及缓冲器电路的运放输入级结构使用了互补差分对的结构, 当输入信号为零, 电路关断的时候, 输出也应当为零, 但在实际的生产过程中, 器件的尺寸在加工的过程中会不同程度的发生误差, 出现不匹配问题。这样就造成了当电路被关闭时仍然有输出的问题, 叫做运放失调。运放的失调由工艺方面的误差造成, 会对性能产生一定的影响, 因而在版图设计的过程中需要充分考虑生产工艺与器件布局对整体电路的影响。对此, 差分对管采用了高宽长比的设计, 降低了沟道寄生影响和随机波动的变化, 提高了匹配度。

对于放大器的电路普遍使用的共源共栅结构以及偏置部分使用的电流镜结构, 由于存在大量尺寸相当的 MOS 管并联, 为了保持版图的紧凑型往往选择将这些 MOS 管集中放置。其排列方式一般使用同心法, 即把所有需要匹配的器件围绕一个中心点分布。该方法在芯片中可以降低模块的热梯度或者工艺的线性梯

度。芯片上流过电流较大的部分会产生发热点，发热点的热量在芯片中扩散，形成热梯度。不同位置的器件距离发热点的距离不同，会使得器件因为所处的温度环境不同而造成性能的偏差。共心法使得器件受热均匀而各部分的性能更为均衡。

对于沟道宽度较大的晶体管如运放功率管和起电容作用的晶体管，为了减小栅电阻和源漏端面积，往往使用交叉法结构。这种方法将串联的两组器件中并联的各部分子器件分别交叉布置，要求所有器件靠近摆放，方向保持一致，但布线的时候会遇到导线相互交叉的问题。这种情况下本文通过使用不同的金属层来解决。考虑到对温度特性的影响，这部分晶体管在布置的时候会尽量远离功率管。通过将匹配的 MOS 管栅极各自相连，可以降低电路的接入电容的大小。因为正方形的面积周长比最大，本文使用正方形设计的电容提高匹配的精确性。

由于 VGMP/VGSP 电压产生电路中使用了大量的电阻串结构用于选择伽马曲线的最高和最低电压，而使用的电阻大小各自不相同，本文使用了根器件法对电阻进行了匹配。在满足设计需求的情况下，将各电阻集中起来平行摆放，使得它们所处的方向保持一致，这样可以消除电阻之间的交叠电容。在电阻中选取一个中间值作为基准将电阻串联和并联，中间值电阻可以降低接触电阻的数量，优化面积消耗。利用这种方法，当所有电阻的尺寸形状一致且相互接近，则匹配性可以达到最佳。通常选定的根电阻越小，匹配越容易，但相应的会提高接触电阻的使用量，电路性能受到寄生电阻的影响，因而本文选择中间值的电阻为根电阻。

而对于线性 DAC 控制下用于输出灰阶电压的电阻串 Rstring1 和 Rstring2 中数量庞大而大小相当的电阻组成的电阻串，本文在设计过程中考虑匹配因素尽量使其各自保持相同的几何形状并集中构成较大的电阻阵列。因为该部分的精度要求较高，本文在电阻阵列两端加入虚拟电阻并远离功率管以形成稳定的独立环境，提高匹配度。

在拐点与输出缓冲器部分有大量传输门结构的 MOS 管与 DAC 相连，这些 MOS 管负责输出灰阶电压以构成伽马曲线。为了提高响应速度往往面积较小，灵敏度要求高，因此对匹配度要求也更比运放部分更高。本文基于工艺的考虑使用虚拟器件法来提高该部分电路的匹配度。在器件的生产加工过程中，光照，离子注入，会因为浓度梯度，扩散程度或者器件的摆放不同而产生各种误差，这导致器件因为工艺的原因而产生失配。为了减小这种误差，需要在器件周围摆放一圈虚拟电阻，这些电阻的尺寸一般与目标器件相同，但不参与连接，只是为目标器件产生一种相对隔绝的环境，以免受周围器件对目标器件构成的工艺误差。

信号线之间的耦合效应以及衬底之间的耦合是影响芯片性能的重要因素。本文在版图设计中为了避免信号线间电容以及衬底噪声的出现，采用了减小信号线交叠面积，保持线与线之间的距离，减小平行线等一系列手段降低了信号串扰对

电路的影响。

由于 NMOS 管与 PMOS 管通常相距不远, 由 PMOS 管有源区, NMOS 管有源区和 N 阵, P 衬底间可能产生闩锁效应。当 PMOS 管的漏级电压发生大的波动, N 阵和 P 衬底将因为正反馈的作用被注入大电流造成器件被破坏甚至烧毁芯片。本文通过在 MOS 管的有源区增加大量接触孔, 降低寄生电阻电容大小, 提高栅极的导通困难程度以避免闩锁效应。

综合以上的设计考虑, 对电路进行版图设计, 在版图设计过程中还需要注意金属走线的宽度。在通过大电流的通路需要把金属线加粗, 因为通过大电流的金属线会发生电迁移现象, 宽度不足容易导致金属线断裂。本文中 LDO 和缓冲器的输入输出均被连接线连至管脚, 因此输出管会受到 ESD 的影响, 因此设计会考虑将漏级加宽, 以提升器件的抗 ESD 功能。

当版图设计完成后, 为了保证版图的可靠性和正确性, 需要通过特定的工具对版图进行验证, 比如是否符合设计规则, 版图与电路是否一致, 是否存在短路, 断路, 悬空的节点。对版图进行全面验证才能使得流片的成功率提高。其中 DRC 和 LVS 验证是最重要的验证环节。集成电路的设计制造必然受到工艺水平的限制, 受到物理器件尺寸的制约。为了保证成品率与电路性能, 要求版图的设计具备一定的设计规则, 这些规则通常由流片的厂家提供。设计规则主要包括各层之间的最小宽度, 最小间距和层与层之间的最小间距和覆盖。LVS 检查则是要保证版图与电路的一致性, 比如器件的类型, 器件的尺寸, 器件之间的互联关系是否正确。

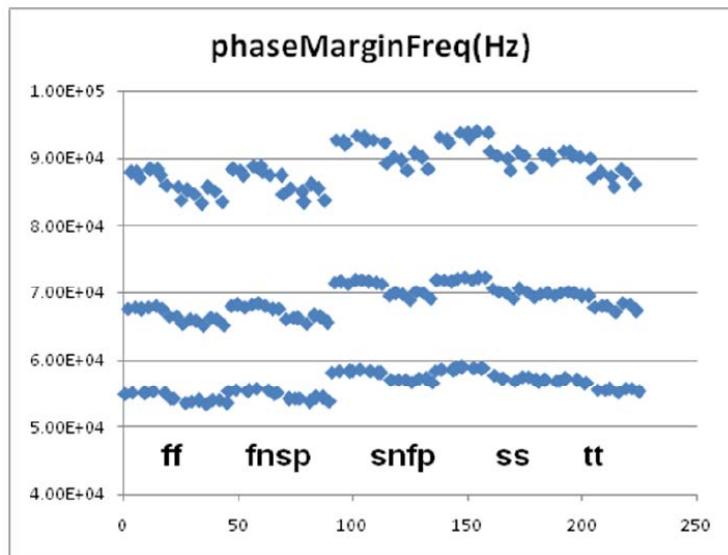

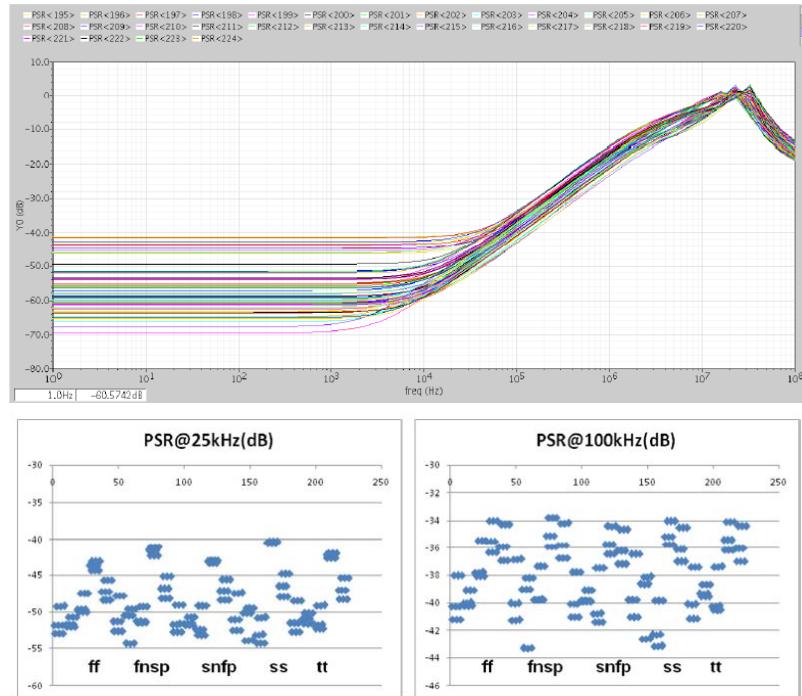

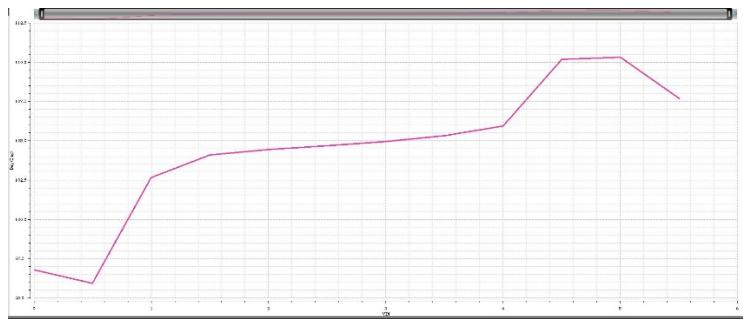

#### 4.5.2 后仿真

本文对 VGMP/VGSP 输出缓冲器电路进行了后仿真, 在仿真环境的输入电压为 5.5V, 电源电压为 DC6V, AC1V。典型工艺角, 偏置电流为 5uA, 负载  $RL=32k\Omega$  时, 电路的 PSRR 如图 4.44 所示。

图 4.44 VGMP 输出缓冲器的 PSRR

Fig 4.44 PSRR of VGMP output buffer

由图中的仿真结果可得, 低频时 PSRR 为 59.15dB, 符合设计指标。在同样的仿真条件下, 对相位裕度进行扫描, 如图 4.45 所示。

图 4.45 VGMP/VGSP 输出缓冲器的相位裕度

Fig 4.45 phase margin of VGMP/VGSP output buffer

由仿真结果可知相位裕度均在 90 度以上, 与前仿结果相吻合。

当输入电压从 0V 到 6V 逐渐变化, 缓冲器的增益图像如图 4.46 所示。

图 4.46 VGMP 输出缓冲器的增益

Fig 4.46 loop gain of VGMP output buffer

由仿真结果可知, 增益均高于 60dB, 符合前仿的设计指标。

在同样条件下对 VGSP 的增益进行扫描, 所得结果如图 4.47 所示。

图 4.47 VGSP 输出缓冲器的增益

Fig 4.47 loop gain of VGSP output buffer

由仿真结果可知，增益基本都在 60dB 以上，符合前仿的设计指标。

#### 4.6 本章小结

本章在对各功能电路进行仿真后可以发现，VGMP/VGSP 电压产生电路能够实现电压的稳定输出，VGMP/VGSP 输出缓冲器准确的输出了电阻串部分所需的高低电平，拐点与输出缓冲器提升了灰阶电压的驱动能力用以驱动较大的后级负载。最后对伽马校正电路整体进行了级联仿真验证，仿真结果证明了电路的设计完全符合设计指标。

## 第五章 总结与展望

### 5.1 总结

AMOLED 以其相比于传统屏幕更多的优势在如今的移动设备显示领域得到了越来越广泛的运用。随着技术的飞速提高以及实现手段的多样化，更大的屏幕和更高的分辨率也成为可能，这对 AMOLED 驱动电路提出了更高的要求。伽马校正是 AMOLED 驱动电路的重要组成部分，也对 AMOLED 的显示效果有着重要影响。

本文针对分辨率为  $1080 \times 2220$  的 AMOLED 显示屏驱动电路，设计了高性能伽马校正电路，主要工作内容有：

- (1) 对 AMOLED 驱动芯片的总体结构做了个简要概括。了解各部分的功能以及对系统的影响，分析系统对伽马校正电路的要求，对比不同的伽马校正方式，确定最适合本文的伽马校正方案作为最终设计，并结合各部分的精度，反应速度要求，从上到下的确定关键电路的参数和设计指标。

- (2) 详细分析了伽马校正各部分电路的功能和设计特点，包括 VGMP/VGSP 电压产生电路，这种电路通过采用轨到轨输入结构具备了较宽的共模输入范围。VGMP/VGSP 电压输出缓冲器电路利用跨导恒定设计获得了在高输入电压摆幅下对大负载的稳定驱动能力。伽马拐点与输出缓冲器电路则通过使用 class AB 输出级获得了灰阶电压快速建立的能力，而 cascode Miller 补偿方式的使用大大降低了该电路占用的芯片面积。最后基于 UMC 80nm 工艺对电路进行了仿真验证，通过仿真得到的各项指标证明电路的性能已经达到了预期目的。

### 5.2 展望

本文对 AMOLED 驱动芯片中的伽马校正电路进行了设计与仿真。设计的电路可以使源极驱动电路高效，迅速而准确的输出系统所需的灰阶电压，但仍有许多可以改进完善之处：

- (1) 受限于项目进度，本文并未完成流片后的最终测试，剩下来的工作将在以后完成。

- (2) 随着显示技术的迭代进步，将来会出现显示效果更佳，物理属性更为多样的屏幕。消费者对显示效果的需求也会更为挑剔，这对伽马校正电路的性

能提出更高的要求，如何实现更高的精度以及响应速度，是接下来需要进一步研究和探索的课题。另外，缓冲器的数量随着精度的提升会变得越来越多，输出电压的精度也需要得到增强。而这不可避免的会带来功耗的提升。功耗、精度、速度的较好折中也是需要在接下来的工作中加以考虑。

---

## 参考文献

- [1] 戴亚翔. TFT-LCD 面板的驱动与设计[M]. 台湾: 台湾五南文化事业出版公司, 2006.

- [2] 马群刚. TFT-LCD 原理与设计[M]. 北京: 电子工业出版社, 2011.

- [3] Hiroshi Kanno, Yuji Hamada, Hisakazu Takahashi. Development of OLED With High Stability and Luminance Efficiency by Co-Doping Methods for Full Color Displays[J]. IEEE Journal of Selected Topics in Quantum Electronics. 2004, 30-36.

- [4] 滕枫. 有机电致发光材料及应用[M]. 北京: 化学工业出版社, 2006.

- [5] 陈金鑫, 黄孝文. OLED 有机电致发光材料与器件[M]. 北京: 清华大学出版社, 2007.

- [6] Y. Matsueda, Y. S. Park, and S. M Choi. 6-bit AMOLED with RGB Adjustable Gamma Compensation LTPS TFT Circuit. SID'05 Digest, 2005, 1352-1356.

- [7] 陈文杰. QVGA AM-OLED 像素电路及集成一体化周边驱动电路的研究与设计[D]. 长春: 吉林大学, 2005.

- [8] C. W. Tang, S. A. Van Slyke. Organic electroluminescent diodes[J]. Applied Physics Letters, 1987, 51(12): 913-915.

- [9] Kim, Eui Tae. Digital Gamma Correction System and Method. United States Patent 8542256, 2013, 24, G09G5/10.

- [10] Haeng Won Park, Seung Woo Lee, Young Gi Kim, Jong Seon Kim, Byeungwoo jeon, Jun Souk. A Novel Method for Image Contrast Enhancement in TFT-LCDs: Dynamic Gamma Control (DGC) . SID, 2003.

- [11] Kaida Xiao, Chenyang Fu, Dimosthenis Karatzas, Sophie M Wuergler. An Improved Method of Visual Gamma Correction for LCD Displays[J]. Display, 2011, 32, 1:17-23.

- [12] Seung Woo Lee, Junpyo Lee, Taesung Kim, Brian H. Berkeley, Sang Soo Kim. RGB Gamma Curve Control for Improved LCD Color Performance. SID, 2006.

- [13] T. Itakura et al. A 402-Output TFT-LCD Driver IC With Power Control Based on the Number of Colors Selected. IEEE Journal of Solid-State Circuits, 2003, 38(3):503-510

- [14] Jang Woo Ryu, Ey Goo Kang, Hyung Seok Park. A Design of AM-OLED Source Driver with reduced Programming Time for a Large Scale Display Panel. IEEE

---

Conference on Electron Devices and Solid-State Circuits,2005,475-477

- [15] Soo-yang Park, Sang Hee Son, Won Sup Chung. High Voltage High Speed Low Power Rail-to-Rail Source Driver for 8-bit Large TFT LCD Applications. IEEE Transaction on Consumer Electronic, 2007,53(4):1589-1594

- [16] Po-Ming Lee, Hung-Yi Chen. Adjustable gamma correction circuit for TFT LCD. IEEE International Symposium on Circuits and Systems, 2005,1:780-783

- [17] Chuen-Chi Yeh, Jia-Hui Wang, Chien-Hung Tsai. A compact low-offset voltage and low power rail-to-rail output buffer for TFT-LCD panel. Proceedings of the International Symposium on Integrated Circuits, 2009, 372-375

- [18] 姚军财, 何军锋, 申静, 谭毅, 黄新民, 赵长水. Gamma 值对 LCD 显示器色彩影响的实验研究[J]. 陕西理工学院学报(自然科学版), 2008, 3:76-79.

- [19] 叶达文. TFT 光电曲线 GAMMA 校正[D]. 哈尔滨工业大学, 2012.

- [20] 姜亨润. TFT LCD 伽玛曲线设计与调校之研究[D]. 台湾科技大学, 1996.

- [21] Martin Kykta, 代永平. 高清显示中的伽马校正、亮度和明视度探索[J]. 现代显示, 2009, 12:13-18.

- [22] K.V.Sakariya. Current Programmed Backplanes for Amorphous Silicon AMOLED Displays[D]. Waterloo, Ontario, Canada, 2006.

- [23] C.W.Tang. An Overview of Organic Electroluminescent Materials and Devices[J]. SID International Symposium, 1996, 5: 11-14.

- [24] B.Young. Will OLEDs Replace Small TFT-LCDs[J]. SID International Symposium, 2005:22

- [25] J.N. Bardsley. 4th Annual China International OLEDs Summit[R]. Shanghai, 2015.

- [26] G.Gu. Design of Flat-panel Displays Based on Organic Light-emitting Devices[J]. IEEE Journal of Selected Topics in Quantum Electronics, 1998, 4:83-99.

- [27] Aerts, W. F. Verlaak, S. Heremans, P. Design of an organic pixel addressing circuit for an active-matrix OLED display. IEEE Trans[J]. on Electron Devices, 2002, 2124-2130.

- [28] Chen Xin Fa, Si Yu Juan, Zhao Yi. A New AC Driving Method for Active-Matrix OLED Displays. Materials Science Forum, 2005, 475-479.

- [29] 司玉娟, 冯凯, 郎六琪. 一种有源有机发光显示屏(AM-OLED)驱动电路的设计[J]. 发光学报, 2005, 257-261.

- [30] Sanja Juric, Vedran Klepac. Gamma and Gamma Correction in Television Production. 51<sup>st</sup> International Symposium ELMAR-2009. 2009, 83-86.

- [31] 陈宏. 用于 AM-OLED 驱动芯片的驱动电路设计与优化[D]. 成都: 电子科技

---

大学, 2010.

- [32] 王颖, 于奇. 高分辨率 AMOLED 显示屏源极驱动电路设计[D]. 成都: 电子科技大学, 2015.

- [33] 童振霄, 王向展. 高分辨率 AMOLED 显示屏源极驱动电路的研究与设计[D]. 成都: 电子科技大学, 2014.

- [34] LEE P M, CHEN H Y. Adjustable Gamma Correction Circuit for TFT LCD [C]. IEEE International Symposium on Circuits and Systems. Kobe, Japan. 2005: 780-783.

- [35] BAE J Y, SEOL H C, KWON Y C, et al. A Small Area 10-bit Linear Gamma DAC with Voltage Adder for Large-Sized Active Matrix Flat Panel Displays [C]. IEEE ISIC. London, Europe. 2014:496-499.

- [36] HUANG T, LI H G. Based on Programmable Current Buffer 10-Bit DAC for AMOLED Source Driver[C]. IEEE/IET Electronic Library(IEL). Hsinchu, Taiwan. 2017:1-2.

- [37] Ron Hogervorst, John P. Tero, Rund G. H. Eschauzier, et al. A Compact Power-Efficient 3 V COMS Rail-to-Rail Input/Output Operational Amplifier for VLSI Cell Libraries[J]. IEEE Journal of Solid-State Circuits. 1994, 1505-1512.

- [38] Johan H. Huijsing, Ron Hogervorst, Klaas-Jan de Langen. Low-Power Low-Voltage VLSI Operational Amplifier Cells[J]. IEEE Trans. on Circuits and Systems. 1995, 841-852.

- [39] Changku Hwang, Ali Motamed, Mohammed Ismail. Universal Constant-gm Input-Stage Architectures for Low-Voltage Op Amps[J]. IEEE Trans. on Circuits and Systems, 1995, 886-895.

- [40] M. Wang, T. L. Mayhugh, S. H. K. Embabi et al. Constant-gm Rail-to-Rail CMOS Op-Amp Input Stage with Overlapped Transition Regions[J]. IEEE Journal of Solid-State Circuits, 1999, 148-156.

- [41] J.M. Carrillo, R.G. Carvajal, A. Torralba. Rail-to-rail low-power high-slew-rate CMOS analogue buffer. Electronics Letters, 2004, 40(14):843-844.

- [42] Willy M.C.Sansen. Analog Design Essentials[M]. New York:Springer-Verlag New York Inc,2006.

- [43] B.Razavi.Design of Analog CMOS Integrated Circuits[M]. New York:Mc Graw-Hill New York,2001.

- [44] P. R. Gray. Analysis and Design of Analog Integrated Circuits[M].USA:John Wiley and Sons,Inc.2009.

---

[45] Changku Hwang, Ali Motamed, Mohammed Ismail. Universal Constant-gm Input-Stage Architectures for Low-Voltage Op Amps. *IEEE Transactions on Circuits and Systems*, 1995, 42(11):886-895.

[46] 陈宏, 于齐等. 一种用于轨到轨运算放大器的新型频率补偿结构[J]. *微电子学*, 2011, 41(1): 15-18.